仕事で役立つ人気ビジネスアプリおすすめ!

[PR]

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

NECエレ、超解像を搭載するシステムLSIを発表

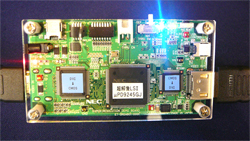

NECエレクトロニクスは11月6日、NEC中央研究所と共同で開発した独自の超解像技術「1枚超解像技術」を搭載したシステムLSI「μPD9245GJ」を開発したことを発表した。サンプル出荷は、2008年12月から、量産出荷も同月中から開始する予定。サンプル価格は3,000円。

「μPD9245GJ」(中央)を搭載した評価ボード

静止画、動画ともに、高画素化、大画面化が進みデータ量の増大が問題となっている。また、あらゆる機器にモニタが搭載され、さまざまな画像を映し出すようになっているが、低解像度の画像データを高解像度の表示パネルに映すとあらが出てしまい、画像にぼやけやギザギザ(ジャギー)が生じるといった問題があった。

そのため、画像処理を行うためには、データが多くても遅延なく高速に処理する能力、拡大処理によるぼやけた画質を改善する能力、組込機器での使用も可能な小型、低消費電力性能などが求められるようになっている。

超解像度技術は、一般的な画像拡大処理(バイリニアやバイキュービックなど)を行った場合に生じる画像のボケやエッジの粗さを改善し、画像拡大処理を行っても解像感が得られる技術。同社の1枚超解像度技術は、従来の超解像技術が、画像のフレーム・データを”複数枚”用いて処理するために、大容量のメモリを必要としてのに対し、”1枚”のフレーム画像から最小限のメモリのみで超解像処理を実現する技術。

1枚超解像技術を用いることで、エッジの粗さやぼやけが改善される、

NECエレクトロニクス 第一SoC事業本部 副事業本部長 金井徹郎氏

これにより、「省メモリで画質の向上が可能なほか、1枚処理のため処理量が少なくリアルタイムでの動画処理が可能」(NECエレクトロニクス 第一SoC事業本部 副事業本部長 金井徹郎氏)とするほか、「補間やエッジ強調などの解像感のアップを1枚の画像入力だけで、しかも表示パネルの前段に挿入するだけで実現することができる」(同)とする。

活用方法は色々とあるが、例えば、DVDなどで録画したSDの画像をフルHDの大画面パネルに表示させようとすると、映像出力側と表示機器側で表示サイズに6倍のギャップが生じるため、ぼけ感やジャギーなどが発生する。超解像技術を活用することで、解像感を維持しながら高解像映像に変換することが可能となる。

超解像を用いることでSD画像を高画質化することが可能となる

また、ビデオカメラなどでは、録画時のデータの圧縮率を上げることで録画時間を延ばすことができるが、画質も必然的に落ちてしまう。それを超解像技術を用いることで、高画質な画像としての再生をすることが可能となる。

ビデオカメラなどで録画した画像の圧縮率を上げても、再生時に超解像を用いることで高画質化することができる

プロセスは0.15μmを採用しており、最大画素数はSXGA(1280×1024ピクセル)/60fpsもしくはHDTV(1366×768ピクセル)/60fpsに対応する。0.15μmプロセスを選んだ理由は「色々とあるが、カスタマから早く使いたいという声に応えるためにこのプロセスを選んだ」(同)とのことである。

製品の概要

また、同技術についてはIPとしての提供も行っており同社のASICにも搭載されるほか、同社のデジタルAV機器向けシステムLSI製品群「EMMA」への搭載も予定しており、2009年度中には発表するという。次世代製品の開発も進めており、フルHD(1920×1080ピクセル)への対応やカラー10ビット対応などが行われ、2009年第2四半期に製品化を見込んでいる。

なお、同社では、同技術を用いたシステムLSIやIPコアの販売を推し進めることで、2010年4月にはシリーズ全体で月産100万個体制を構築するほか、2010年度に100億円の受注を目指すとしている。

左が拡大処理のみをした元画像で、右が1枚超解像を用いて処理をした画像()

富士通研、32nm以降に対応した低消費電力化CMOS技術を開発

富士通研究所は12月16日、32nmプロセス以降のロジックLSI向けに、低消費電力化CMOS技術を開発したことを発表した。

従来、トランジスタの電源電圧を下げると、MOSトランジスタが流すことができるオン電流が減少し、動作速度の低下を引き起こす問題があった。

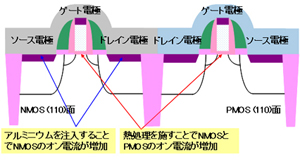

今回開発された技術は、既存の45nmプロセス世代の設備に、結晶面(110)面のSi基板を適用することで、既存の(001)面と比較して、NMOSのオン電流を減少させることなく、PMOSのオン電流を向上させることが可能になるというもの。

32nm世代以降向け低消費電力化CMOS技術

Siの表面処理として、ゲート絶縁膜形成前に施す熱処理時に通常とは異なるガスを用いて熱処理を行うことで、素子分離領域近傍に(111)面と(331)面を形成することに成功した。いずれの面のNMOSの移動度は(110)面の移動度よりも高いため、ゲート中央部が(110)面であっても、オン電流は10%の向上となる。また、PMOSのオン電流も移動度の向上により10%の向上が確認された。

トランジスタのゲート幅方向の断面と結晶面の関係

また、シリサイドの形成後にAlを注入することで、NMOSのシリサイドとSiのコンタクト抵抗が減少することを発見。Alをシリサイドの極浅領域に注入することで、NMOSのオン電流の20%向上を実現した。さらに、Siの表面処理技術と併用することで、(110)面のSi基板を用いても、(001)面と同等のNMOSのオン電流を実現した。

一方、PMOSのコンタクト抵抗はAlの注入により増加し、PMOSのオン電流が減少することも判明。そのため、NMOS領域に選択的にAlを注入するプロセスを構築し、PMOSのオン電流減少を防いだ。

今回開発された技術と従来技術の比較

これらの技術を用いた(110)面のSi基板採用LSIを試作した結果、従来の(001)面の場合に比べ、NMOSのオン電流を維持したまま、PMOSのオン電流を40%向上できることが確認された。これにより、電源電圧を10%下げても、動作速度は低下せずに消費電力が約20%削減できることが確認された。

また、同技術を45nmプロセスの製造工程に導入した場合、追加される工程はイオン注入と熱処理の2工程のみであり、32nmプロセス以降の製造工程に導入した場合でも、ウェハコストを除いた製造コストは1%以下の増大で抑えることができるという。

同社では、32nmプロセス以降の携帯機器向けシステムLSIやマルチコア・マイクロプロセッサなどへの適用に向け、実回路での評価を進めていくとしている。

富士通研ら、CMOSプロセス採用パワーアンプ向け高耐圧トランジスタを開発

富士通研究所ならびに富士通マイクロエレクトロニクスは12月17日、CMOSロジックプロセスを用いたワイヤレス機器用パワーアンプ向け高耐圧トランジスタを開発したことを発表した。

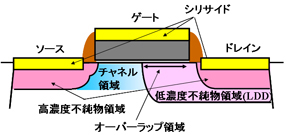

従来、WiMAXなどの高周波向けパワーアンプに要求される出力電圧を実現するためには、通常のCMOSロジックプロセスによるトランジスタでは耐圧が不十分であった。そのため、CMOSロジックプロセスとの親和性を保ちながら、トランジスタの破壊につながるドレイン付近の電界を緩和させた構造を採用し、トランジスタの高耐圧化を行う必要があった。また、従来の高耐圧構造はトランジスタのオン抵抗を上昇させてしまう問題も抱えていた。富士通研らは、トランジスタのドレイン側に不純物を低濃度で注入した領域(LDD:Lightly Doped Drain)を形成し、その領域をゲートとオーバーラップさせることで、ドレインに加わる横方向の電界とゲート酸化膜に加わる電界を緩やかにし、耐圧の向上を実現した。

また、トランジスタのチャネルの不純物分布を、横方向に勾配を持たせることにより、ドレイン側のチャネル不純物濃度を低減させ、オン抵抗の主要因であるドレイン抵抗の上昇を抑制、同時にドレインに加わる横方向の電界の低減により、耐圧を向上させた。

開発したトランジスタの構造

これらの技術を採用したトランジスタは、従来のCMOSトランジスタの耐圧向上技術であるゲート/ドレインの間隔を広げる方法と比べても、オン抵抗の上昇を抑えることが可能であることが確認された。

製造方法については、通常の3.3VのI/Oトランジスタの製造工程に、LDD領域の形成工程と専用チャネル領域の形成工程を追加のみで製造が可能。

今回、45nmプロセスの製造技術を用いて、通常の3.3VのI/Oトランジスタに同技術を適用したところ、耐圧を6Vから10Vに引き上げることに成功。トランジスタ特性としては、最大発振周波数が43GHzで、ゲート幅1mmあたり0.6Wの最大電力を達成したほか、基本的な信頼性評価でも良好な結果が得られたという。

パワートランジスタの特性(測定周波数2.1GHz, ゲート幅0.32mm)

今後、両社は、同技術の発展を目指し、パワーアンプと制御回路の1チップ化を図ったパワーアンプモジュールの提供を目指すとしている。

Intel、Siを用いたAPDを開発

Intelは12月7日(現地時間)、同社研究開発部門「Intel Labs」において、SiをベースとしたAvalanche Photodetector(APD)を開発、同素子で340GHzのGain x Bandwidth(GB:利得帯域幅)積を実現したことを発表した。

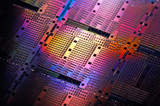

今回製作されたAPDのウェハ

素子のサイズをてんとう虫と比較

パッケージ化されたAPD(左)とその拡大画像(右)

APDは、通常のPhotodetector(PD)が、1つの光子の入力に対し1つの電子を出力するのに対し、固体内で発生した電荷が結晶格子を構成する原子に衝突するごとに電離を引き起こすことで電荷を増幅していく様子がさながら「Avalanche(なだれ)」のようであることからつけられたPD。このため、1つの光子の入力によって、通常のPDと比べ10倍~100倍程度の電子を出力することが可能となる。

左が従来のPD、右がAPDによる動作図

これにより、Intelのフォトニクス・テクノロジー・ラボ ディレクターで、IntelのフェローであるMario Paniccia氏は、「通常のPDが10mWのレーザを受光できる距離を1とすると、APDでは同じ距離なら出力を1/10程度に、また同じ出力なら距離を10倍に増やすことができる」と語る。

今回Intelが開発した素子は、従来InPなどの化合物半導体で用いられていたものを、上層の光子を吸収するAbsorption RegionにGeを用い、下層のMultiplication RegionにSiを用いたというものでSiとGeによる歪み技術が用いられている。

IntelのSiベースAPDの構造

SiとGeによる歪み技術

これにより、GB積で従来にInPによるAPDと比べ2倍以上となる340GHzを達成しており、利得を30倍にしても10GHz帯での利用が可能になるという。

GB積の関係(InPのAPDとの比較)

同研究には、Intelのほか、米国防高等研究計画局(DARPA)が出資、米Numonyxが製造とプロセス技術の面での支援、米バージニア大学のジョー・キャンベル教授と米カリフォルニア大学サンタバーバラ校のジョン・バウワーズ教授がコンサルタントとして参加している。

なお、Intelでは、同研究に関しては、「仮に実用化すれば、現在300ドル程度のAPDを100ドル程度まで下げることを狙える」(同)とするが、まだ研究開発のものとしており、市場への展開などに関しては未定としている。

Alteraから40nmプロセス採用FPGAがついに出荷

幅広い分野での活用を期待

幅広い分野での活用を期待

Alteraは12月15日(米国時間)、40nmプロセスを採用したFPGA「Stratix IV」の出荷を開始したことを発表した。同ファミリのターゲット市場は通信、放送、テスト機器、医療機器、軍用などとしており、ハイエンドな性能が求められる幅広い分野での活用が期待される。FPGAとして、初めて40nmプロセスを採用した同ファミリの性能とはどのようなものか、製品に込められた同社の想いも含め、日本アルテラ マーケティング部 ディレクタの堀内伸郎氏に話を聞いた。

日本アルテラ マーケティング部 ディレクタの堀内伸郎氏

同ファミリの話をする前に、同社のFPGA「Stratix」について少々触れておく必要がある。Stratixが登場したのは2002年、その後2004年に90nmプロセスを採用した「Stratix II」を、2006年に65nmプロセスを採用した「Stratix III」をそれぞれ発表してきた。そのStratixシリーズの新ファミリとして登場したのがStratix IVだが、これには高速トランシーバを内蔵した「Stratix IV GX」と非搭載型の「Stratix IV E」の2種類がラインナップされる。

ちなみにStratix IIIのラインナップは、多数のロジックを搭載するアプリケーション向け品「Stratix III L」とDSPおよび大容量メモリ使用のアプリケーション向け品「Stratix III E」の2種類となっている。また、Stratix IIには、無印品とオンチップトランシーバを搭載した「Stratix II GX」の2種類が用意されている。

つまり、Stratix IV GXはStratix II GXをより高性能化したもの、Stratix IV EはStratix III Eをより高性能化したものともいえる。GXはIIIでの提供をスキップしてIVでの提供となっているが、これに関して堀内氏は、「実はStratix IIIの発表時には、GXの提供も予定していた」と語る。しかし、すでにStratix II GXで6.375Gbpsまでの帯域をサポートしており、「IIIでGXを開発した場合、どのような性能が求められるのか、また提供時期が何時ごろになるかを検討した」(同)、その結果として、Stratix IIIでGXを提供しようとすると2008年での提供になってしまうとの結論が出たという。

Stratix IV GX「 EP4SGX230」のウェハ(左)とダイ(右)(画像提供:日本アルテラ)

また、社内では「TSMCとの共同プロセス開発の進捗状況を見て、予想よりもStratix IVの立ち上がり時期が早まりそうだと感じていた」(同)としており、2008年の第4四半期にStratix IVが提供を開始されたことを考えれば、その差が1~2四半期程度しかなく、製品の差別化が困難になることから、Stratix IIIでのGX提供をスキップしたという。

そのため、Stratix IVは、これまでのStratixシリーズで採られてきた通常版のStratixの提供の後に、GX版の提供という手順を変えて、先にStratix IV GXの提供を行い、その後Stratix IV Eの提供を行うとしている。

これは、「市場的にはGbps帯域のトランシーバを持つチップの需要が増えていくとの予測」(同)が働いているためでもあるとしており、特にPCI Express Gen2.0への対応が進むと見ている。PCIe Gen2.0ならば5Gpbsの伝送速度であるため、Stratix II GXでも一応の対応は可能だが、「サポートはできなくはないが、ジッタ性能が厳しい点や、プロトコルサポートのため内部回路を後から組み込む必要がありタイミング設計が収束しない問題も生じかねないという点、それによる内部回路の使用量が大きくなってしまうという点」(同)がチャレンジであり、デモ程度なら使用可能だが、一般には実用的ではないという。

Stratix IV GXでは、8.5Gbpsまでサポートしているが、始めから、前述のような回路などを内包しており、余分な問題などが生じないようになっている。また、「もしStratix IIIでトランシーバを搭載しても10Gbpsに対応するのは困難だったかもしれないが、Stratix IVでは非公式だが、10Gbpsオーバーのポテンシャルがある」(同)ということもIVにスキップした理由だという。