仕事で役立つ人気ビジネスアプリおすすめ!

[PR]

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

アバールデータ、Atom搭載CompactPCIバスモジュールを発売

アバールデータは、同社のCompactPCIモジュールである「ACPシリーズ」にAtomプロセッサを搭載したCompactPCIバス対応CPUモジュール「ACP-162」を開発、販売を開始したことを発表した。

CPUモジュール「ACP-162」

同モジュールは、CompactPCI 3Uタイプのモジュールで、幅広い用途での使用を考慮し、CPU部(CPUボード)とI/O部(ベースボード)を分けた2枚の基板で構成されている。これにより、機能の追加などカスタマからの要求仕様に”短納期・低コスト”で対応することが可能となるという。

搭載可能メモリはDDR2 SDRAMで、最大2GBまで対応する。また、1000Base-Tのイーサネットを2チャネル、USB2.0を3チャネル、RS232Cを1チャネル、DVI-Dを1チャネル、シリアルATA1チャネルなどを搭載している。

対応OSはWindows XPおよびLinux。

主な製品の応用分野としては、半導体製造装置、生産ラインの制御機器、検査分析機器、計測機器、試験装置などが想定されている。

コンピュータアーキテクチャの話 (138) キャッシュアクセスの2つの考え方

キャッシュアクセスの構造

キャッシュアクセスの構造

プロセサからメモリアクセス要求が出されると、そのアドレスのデータがキャッシュメモリに格納されているかどうか、格納されている場合は、どのキャッシュラインに入っているかを高速に判定する必要があるが、キャッシュはメインメモリのあちこちのアドレスのデータを格納するので、これは必ずしも簡単ではない。

このやり方として、大きく分けて2つの考え方がある。1つは、プロセサからアクセス要求が出されたアドレスと、キャッシュ内のすべてのキャッシュラインのタグを比較し、上位アドレスが一致したラインがあればヒットであり、そのキャッシュラインのデータを使うという方式である。

この方式は、検索方法としては理想的であるが、すべてのタグに比較回路を付ける必要があり、ハードウェアの物量と消費電力が大きい点が問題である。

もう1つの考え方は、アドレスの一部をインデックスとして使用し、あるアドレスのデータとタグのペアは、キャッシュの固定した部分にしか格納できないという制約を付け、探索範囲を1カ所から数カ所程度に限定することにより検索を容易にする方式である。

この方式は検索は容易であるが、メインメモリ上のアドレスにより使用できるキャッシュラインが決まってしまうので、キャッシュの利用率が低下し、ヒット率が低下するという問題がある。

フルアソシアティブキャッシュ

この理想的に、すべてのキャッシュラインのタグとプロセサからアクセス要求されたアドレスを比較するのがフルアソシアティブ(Full Associative)キャッシュ、あるいは連想キャッシュという方式である。

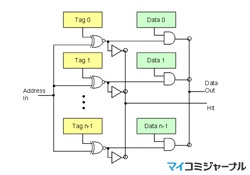

図4.5 Full Associative Cacheの構造

フルアソシアティブキャッシュは、図4.5に示すように、それぞれのタグの上位アドレス部とプロセサからのアドレスの一致を検出する回路を設け、一致したキャッシュラインはAND回路を開いて、そのデータ部の内容を出力する。

なお、図4.5では通常のXOR回路が書かれているが、この部分はタグの上位アドレス部の数十ビットの一致を検出する回路が必要となる。また、データアレイの出力側のAND回路は、データアレイのサイズだけのビット幅の並列のAND回路が必要である。また、図中の○はOR機能をもつ接続(Wired OR)を示している。

そして、一致回路の出力をバッファしてWired ORすることにより、プロセサからのアドレスがキャッシュ内に存在したというヒット状態を示す信号を生成している。このヒット信号が”1″の場合はデータ出力を使用し、この信号が”0″の場合は、どのキャッシュラインのタグとも一致しなかった、つまり、キャッシュ内に要求されたデータが存在しないことを意味しているので、この信号を使ってメインメモリ(あるいは下位のキャッシュ)へのアクセス動作を開始する。

このフルアソシアティブキャッシュ方式は、どのキャッシュラインにもメインメモリ上の任意のアドレスのデータを格納することができ、格納位置の自由度が高いという利点があるが、タグの比較回路がチップ面積、消費電力の点で大きな負担になるという問題点がある。このため、ライン数が多い大容量のデータや命令キャッシュとしてフルアソシアティブキャッシュ方式のキャッシュが用いられることは稀である。

一方、小容量のキャッシュでは、格納位置の自由度が高く、総メモリ容量の割りにはヒット率が高いという利点があり、後述のアドレス変換テーブルなどのプロセサ内の小容量のキャッシュとしては、フルアソシアティブキャッシュ方式が良く用いられている。

日本はあらゆる市場でイノベイティブ

1983年に設立され、今年で設立25周年を迎えたFPGAベンダ大手の米Altera。世界初のプログラマブル・ロジック・デバイス(PLD)「EP 300」を1985年に開発したほか、2008年5月には、40nmプロセスを採用したFPGA「Stratix IV」とASIC「HardCopy IV」を発表するなど、FPGA/PLD業界で常に技術開発の先頭に立ってきた。

同社の特長は、日本でのFPGA/PLDにおけるシェアが高いこと。そして全世界の売り上げに日本が締める割合が20%以上であること、といった具合に日本での活躍が目立つ。

そんな同社の日本法人である日本アルテラ代表取締役社長の日隈寛和氏に、Alteraの現状とFPGA/PLDに関する今後の戦略について話を伺った。

日本アルテラの代表取締役である日隈寛和氏(本社であるAlteraの時代を含めると来年で勤続15年を迎えるという)

――さっそくですが、半導体ベンダであるAlteraが重要視している点はどのようなところにあるのでしょう。

他のデバイスでもそうだと思いますが、市場でカスタマに使用してもらうにはデバイスのアーキテクチャのみならず、開発ソフトウェアツールを用意する必要があります。

Alteraでは、自社でツールのエンジンを開発しています。そこで課題としているのが、いかにカスタマの設計生産性を向上させるか、ということと、デバイスの持つアーキテクチャの性能をどれだけ引き出せるか、という2つのことです。

過去、日本のメーカーを含めて、多くの半導体ベンダがFPGA市場に参入し、撤退していきました。優れたデバイスと優れたツールの双方を開発することは難しく、それが一因ではないかと思いますが、Alteraでは、常にカスタマが使いやすいツールを用意することで、さまざまなニーズに応えてきたことが、現在につながっているのだと思います。

コンピュータアーキテクチャの話 (135) メモリのアクセス時間とローカルメモリ

メモリアクセス時間の短縮

メモリアクセス時間の短縮

ここまでは、メモリは1サイクルか2サイクルでアクセスができるという想定でパイプラインを考えてきたが、この想定がある程度成り立っていたのは30年以上も昔のことである。それ以降の30年で、プロセサのクロックは1000倍程度速くなったが、メモリのアクセスタイムは10倍程度しか向上しておらず、結果として、現在のマイクロプロセサがDRAMで構成されたメモリをアクセスするには、100サイクル以上を必要とするようになってきている。

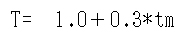

メモリのロード、ストアを行う命令の出現頻度は、典型的なプログラムでは30%程度である。パイプライン処理を頑張って1サイクルに1命令(IPC=1.0)の実行を可能としても、30%の命令でメモリアクセスが必要となると、1命令の実行時間は、

となってしまう。ここでTは平均的に1命令の実行に掛かるサイクル数(Instruction Per Cycle)であり、tmはプロセサのサイクルタイムを単位としたメモリアクセス時間である。

最近のマイクロプロセサでは、サイクルタイムは0.4ns(2.5GHzクロックの場合)程度であり、プロセサコアからのDRAMメモリのアクセスタイムを60nsとすると、tm=150である。そして前述の式にこの値を代入すると、Tは46となる。つまり、実行ユニットは、毎サイクル1命令を実行する能力があるが、メモリアクセスに45倍もの時間がかかり、1秒間に実行できる命令数はクロック周波数の1/46に低下してしまう。

ローカルメモリ

実社会でも、遠くの倉庫まで毎回必要な工具や材料を取りに行くのでは、時間が掛かって仕事の効率は上がらない。近くに小さな置き場を作り、頻繁に使う工具や、次に必要となりそうな材料はまとめて倉庫から持ってきておけば、遠くの倉庫まで行く回数が減り、大部分は近くの置き場まで取りに行けば済む。

これと同じ考え方で、近くに置き場を作り、遠くなってしまった大倉庫であるメインメモリまでアクセスする回数を減らすというのがローカルメモリという考え方である。

メモリアクセスの内のある割合(ここではhとする)が、遠くの倉庫であるメインメモリまで行かずにローカルメモリで済むとすると、前述のTは、

となる。ここでtlはローカルメモリのアクセス時間をプロセサのサイクルタイムを単位として表したものである。仮に、hを0.95、tlを2.0とすると、

となり、平均3.82サイクルで1命令が実行できるようになる。これは、ローカルメモリが無い場合の46と比べると、性能が12倍に向上している。この様子を図4.1に示す。

図4.1 メインメモリ直接アクセスとローカルメモリを使用した場合の平均命令実行サイクル数の比較

少し、話はそれるが、コンピュータのメインメモリが16KB~256KBという時代は、すべてのプログラムやデータをメインメモリに置くことが出来ないので、本体はドラムやディスクといった磁気記憶装置に置き、必要な時にメインメモリに持ってくるオーバレイという手法が使われた。

ローカルメモリは、これと同じ手法をメインメモリとプロセサの間に適用し、メインメモリの内容のうちの頻繁に使用する部分をプロセサに近い小容量だが高速なメモリに持ってきて使うようにしようというものである。

このやり方には、大きく分けて2通りある。1つは、どのデータをローカルメモリに持ってくるかをプログラムが指示する方式で、最近の例では、CELLプロセサの計算エンジンであるSPE(Synergistic Processing Element)のローカルメモリがこの方式である。もう1つの方式は、ハードウェアがどのデータが頻繁に使われるかを判断して、ローカルメモリに自動的にデータを出し入れする方式である。

エルピーダの2009年3月期中間期決算

エルピーダメモリは11月6日、2009年3月期第2四半期(7-9月期)ならびに中間期(4-9月期)の決算概要を発表した。第2四半期の業績は、売上高が歩留まりおよび生産性の改善により前年同期比1.8%増の1136億円としたものの、PC向けDRAMの価格下落などの影響を受け、営業損益は前年同期の61億円の利益から245億円の損失へと転落した。また、純損益も同33億円の利益から319億円の赤字へと転落した。

エルピーダメモリの2009年3月期第2四半期の業績

これに伴い、中間期の業績は、売上高が同0.8%増の2,228億円、営業損益が同98億8,300万円の利益から401億600万円の損失に、純損益が178億2,800万円の利益から456億4,200万円の損失へとそれぞれ転落した。

第2四半期の業績の主な要因となったDRAM価格だが、例えば1GビットのDDR2 667Mbps品は7~8月にかけては緩やかに下落していたが、9月に大きく下落したことが影響したという。また、その後もDRAMのスポット価格は下落が続いており、11月5日段階で0.97ドルまで下落している。ただし、同第2四半期のビット成長率は、Rexchip Electronicsの生産性の改善などにより、前四半期比で13%増となった。

1Gビット DDR2 667Mbpsのスポット価格推移

また、同社代表取締役社長兼CEOの坂本幸雄氏は、10月14日に発表した資金調達(PDF形式)について言及、「”一寸先がまったく見えない”という市況に対して手元流動性を高めておきたかった」とした。

その主な要因としては2つある。1つは、不況期においても競争力を確保するためのプロセスの微細化を実現するたの最低限の投資を可能とするため。もう1つは、不透明なDRAM不況ならびに金融不安が長期化した場合に、それを耐え切れる財務基盤の確保のため。

資金調達により投資費用の確保と財務基盤の強化を実施

このほか、坂本氏は2009年の設備投資にも触れ、エルピーダでは65nmプロセスが95%、50nmプロセスが5%の製品割合へとシフトさせ、好況時のオプションとして65nmを60%、50nmを40%へと変更することもあるという。また、Rexchipでは、65nmが70%、50nmが30%の比率とし、好況時のオプションとして65nmを50%未満、50nmを50%以上へと変更する可能性も持たせるとした。

2009年度の設備投資の方針

また、複数の半導体メーカーと進めている提携関係についても触れた。中でも、台湾United Microelectronics(UMC)との提携によるCu配線技術は大きな収穫だったとし、50nmプロセスでの使用を予定している。一方、中国のベンチャーキャピタルであるSuzhou Ventures Group(蘇州創業投資集団:SVC)と進めている中国蘇州市での合弁工場については、「建設から稼働まで2年は見積もる必要がある。その間、キャッシュが寝ることとなり、現在の市況にそぐわない」(同)とし、1年程度もしくは市況回復の見込みが立つまで工事を遅らせることを決定したとした。ただし、将来を考えると、中国での生産は必要であるとしており、市況を見ながら検討を進めるとした。

現在進められている提携内容の一覧

さらに、具体的な話は明らかにしなかったが、Rexchipをエルピーダの連結子会社化する方向で検討が進んでいること、ならびにPowerchip Semiconductor(PSC)との資本提携なども含めた提携強化策を模索していくことも明らかにした。特にRexchipの連結子会社化は、2009年第1四半期中に実行する予定とした。

Rexchipの連結子会社化などを検討

なお、グローバルにみたDRAMの生産能力の内、200mmウェハ工場で生産させる割合は全体の13%(300mm換算)と見込まれるが、現在各社ともに閉鎖を進めており、「その廃止コストが相当かかるはず」(同)とした(同社は2007年に200mmの処理装置を売却済み)ほか、「もし200mmのラインがなくなったら、需要と供給のバランスは十分に引き締まるのではないか」(同)との考えを明らかにし、「日本産業の中にDRAM、NAND型フラッシュメモリが必要か否かが問題となってくる。このまま韓国や欧米、台湾のDRAMメーカーに国内市場をとられたら、日本の産業がどうなるか、という問題にまで発展する」(同)とし、不況に対しても十分に対応していけることを強調した。

グローバルでみた場合の各社のDRAM生産能力