仕事で役立つ人気ビジネスアプリおすすめ!

[PR]

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

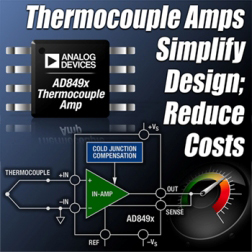

ADI、冷接点補償機能を搭載した熱電対アンプ「AD849x」ファミリを発表

Analog Devices(ADI)は、KタイプとJタイプの熱電対向けに、熱電対アンプファミリ「AD849x」として「AD8494」「AD8495」「AD8496」「AD8497」4製品を発表した。いずれもすでにサンプル出荷を開始しており、単価は1万個受注時でいずれも0.98ドルとなっている。

ADIの熱電対アンプファミリ「AD849x」

熱電対システムは高い精度で温度測定と温度管理を実現するが、最適な測定性能を得るには、冷接点補償機能および高ゲインな高精度のアンプが必要になる。同社が今回発表した4製品は、周囲温度の変化に対して熱電対の出力を自動的に調節する冷接点補償機能を集積することで、これらの課題を解決することが可能なほか、冷接点補償機能により、同類のディスクリート・ソリューションと比較して設計の簡素化が可能となる。

いずれも製品も熱電対より発生する小さな電圧を、A/Dコンバータ(ADC)またはマイコンで読み取ることができ、5mV/℃のアナログ信号に変換することが可能。また、冷接点補償機能による測定保証と同時に、0.1℃/Vの同相ノイズ除去性能により、熱電対の長いリード線に起因する同相ノイズを除去できる。

さらに、いずれも2.7V単一電源から±18V両電源まで動作可能で、静止電源電流消費は180μAを実現しており、単一電源動作では、アンプは低電源電圧のADCに直接インタフェースできるほか、広いコモン・モード入力範囲を必要とする産業用システムには、高い両電源電圧で使用することができる。

FSL、LTEに対応したSAWフィルタ不要のRFトランシーバLSIを製品化

富士通セミコンダクター(FSL)は6月2日、携帯電話向け次世代通信方式LTE(Long Term Evolution)に対応したRFトランシーバLSI「MB86L10A」を発表した。2010年8月初旬よりサンプル出荷を開始する予定で、初年度月産100万個の販売を目指す。

LTE対応RFトランシーバLSI「MB86L10A」

同製品は、従来のGSM/GPRS、EDGEの2G通信方式、W-CDMA、HSPAの3G通信方式への対応機能を1チップに集積、受信部には、LTE、W-CDMA、およびGSM/EDGEをサポートする9つの入力ポートを備え、低雑音増幅器LNA内蔵、GSM受信系を除きSAWフィルタを不要としているほか、UMTS、またはLTEのマルチ受信を可能とする5つの追加入力ポートを搭載、高い受信性能を実現しており、コンパクトなRFトランシーバシステムを実現することができる。

また、ベースバンドLSIとのインタフェースに、従来のMIPI規格であるDigRF Ver3と、LTE用のDigRF Ver4を両方備えることで、DigRF Ver3を持つベースバンドLSIとの互換性と、2G・3G・LTEのベースバンドLSIからDigRF Ver4のインタフェースのみで制御することを可能としている。さらに、2系統の受信系を持つことで通信の安定性と高受信感度を実現した。

LTEの通信方式は、各国に割り当てられている、さまざまに異なる周波数や通信方式のモードを、ファームウェアのみでサポートすることで携帯電話システムの開発期間と工数を低減することが可能。対応するバンドはGSMと各国のUMTSのバンド、LTEのバンドとLTE-TDDもサポートしている。

NS、ゼロレイテンシ制御チャネル内蔵SerDesファミリを発表

National Semiconductor(NS)は、ゼロレイテンシ双方向制御チャネル内蔵チャネルリンクIIIシリアライザ/デシリアライザ(SerDes)ファミリを発表した。

ゼロレイテンシ双方向制御チャネル内蔵チャネルリンクIII SerDesを活用したアプリケーションブロック図の例

同SerDesは1本のツイスト・ペア上で高速クロック・データと低速双方向I2C制御バスを提供することが可能。これにより、産業用ビデオ/画像処理/ディスプレイ・アプリケーションで、従来ソリューション比最大50%のインターコネクト・サイズ、重さ、コストの低減を実現することが可能となる。

同ファミリは2つのデバイスから構成されており、1つはシリアライザ「DS92LX2121」とデシリアライザ「DS92LX2122」の組み合わせで、18ビット・カラーのディスプレイ・アプリケーションまたは最大1050Mbpsのデータ・リンクを駆動することが可能だ。

また、シリアライザ「DS92LX1621」とデシリアライザ「DS92LX1622」の組み合わせでは、最大800Mbpsの16ビット・データを駆動させることが可能だ。いずれのチップセットもロー・ボルテージCMOS(LVCMOS)パラレル・インタフェースを採用しており、10MHzから50MHzで動作することが可能。

いずれもチップセットもサンプル出荷を開始しており、量産品は2010年7月から供給する予定となっている。単価は、1,000個一括購入時でDS92LX2121(40ピンのLLPパッケージ)とDS92LX2122(48ピンのLLPパッケージ)がそれぞれ5.30ドル、DS92LX1621(32ピンのLLPパッケージ)とDS92LX1622(40ピンのLLPパッケージ)がそれぞれ5.10ドルとなっている。

また、同社は併せて、一般アプリケーション向けに双方向の制御チャネルがない2つのチップセットを「チャネルリンクIIファミリ」として発表している。1つはシリアライザ「DS92LV2421」とデシリアライザ「DS92LV2422」で、LVCMOSパラレル・インタフェースを採用している。もう1つはシリアライザ「DS92LV0421」とデシリアライザ「DS92LV0422」で、チャネルリンクSerDesで使用されている小振幅差動信号(LVDS)インタフェースを採用している。このため、DS92LV0421/DS92LV0422はLVDSブリッジ機能を通じて、チャネルリンクSerDesからのアップグレード・パスを提供する。いずれのチップセットも高速データとクロックを組み込み、24ビット・データを最大1.8Gbpsの転送レートで駆動し、10MHzから75MHzで動作することが可能だ。

今回発表されたチャネルリンクIIIおよびチャネルリンクIIチップセットはいずれも、シグナル・コンディショニング機能を内蔵しており、リモート・ディスプレイまでの高速信号の駆動距離を他の一般的なSerDesの2倍に延長することが可能だ。また、産業用アプリケーションの過酷な動作環境でEMI(電磁波障害)を低減するための拡散スペクトル・クロッキングを備えているほか、8kV超のHBM(人体モデル)ESD(静電気放電)耐量を提供、ISO 10605のESD規格に準拠している。さらに、いずれのSerDesファミリも-40℃から+85℃で動作し、リンク整合性を検証するための内蔵自己テスト(BIST)診断機能を備えている。

なお、今回発表されたチャネルリンクIIチップセットもすでにサンプル出荷を開始しており、2010年7月からの量産開始を予定している。サンプル価格は、1,000個一括購入時でDS92LV2421(48ピンのLLPパッケージ)とDS92LV2422(60ピンのLLPパッケージ)がそれぞれ5.95ドル、DS92LV0421(6ピンのLLPパッケージ)とDS92LV0422(48ピンのLLPパッケージ)がそれぞれ6.25ドルとなっており、5MHzから50MHzの低速グレード品もリリース予定となっている。

コンピュータアーキテクチャの話 (199) マルチプロセサで共用されるデータ構造

Load LinkedとStore Conditional命令

Load LinkedとStore Conditional命令

しかし、各プロセサがキャッシュを持っている場合は、話が複雑になる。1つのやり方として、Load Linkedという命令とStore Conditionalというペアの命令を用いる方法がある。この場合は、まず、札メモリをLoad Linked命令で読む。この命令は、指定されたアドレスのデータをキャッシュに読み込み、引き続き、ハードウェアでそのキャシュラインが他のプロセサからアクセスされるかどうかを監視する。そして、プログラムは、読まれた値がゼロの場合は札メモリに対してStore Conditional命令を発行する。この間に、他のプロセサからの札メモリへのアクセスが無ければ、Store Conditional命令は成功し、オペランドで指定されたデータをキャッシュラインに書き込む。

一方、スヌープにより他のプロセサからのアクセスが検出された場合は、Store Conditional命令は失敗し、オペランドのデータは書き込まれない。また、Store Conditionalの成功、失敗は、命令の結果を示すレジスタに通知されるので、この値を見ることにより、プログラムは使用権の獲得の成功、失敗を知ることができる。

ハードウェアとしては、各キャッシュラインにLoad Linked命令で読まれたことを示す属性ビットを設ける。そして、Load Linkedで読まれたキャッシュラインのこのビットをセットし、このアドレスに他のプロセサからのスヌープが来ると、そのビットをリセットする。そして、Store Conditional命令を実行する際に、ビットがセットされたままであれば成功で、Storeを実行し、結果レジスタに成功を書き込む。一方、ビットがリセットされている場合は失敗であり、Storeを行わず、結果レジスタに失敗を書き込むというようにすれば良く、キャッシュコヒーレンス用のスヌープ機構に比較的簡単な追加を行うことで実現できる。

Test and Set命令

また、キャッシュをもつプロセサにTest and Set命令を設ける場合は、メモリを読み、その値がゼロである場合は、オペランドで指定された内容をメモリに書き込むという動作を、間に他のプロセサのメモリアクセスが入らないようにアトミックに実行する必要がある。キャッシュを持つプロセサの場合、Test and Set命令はストア命令と同様に札メモリをキャッシュに読み込み、書き込みのために、他のプロセサのキャッシュラインをスヌープして無効化する。そして、メモリから読まれた値をTest and Set命令の結果として返す。

さらに、通常のストア命令では無条件にキャッシュラインに書き込みを行うが、Test and Set命令の場合は、読まれたメモリのデータがゼロである場合はオペランド値を書き込み、非ゼロの場合は書き込みを行わないようにする。

Compare and Swap命令

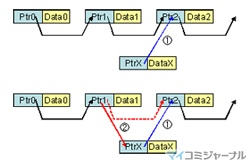

図9.20のようなポインタで要素をつないだリスト構造は、プログラムで良く用いられるデータ構造である。この構造のData1とData2の要素の間にDataXを挿入する場合、まず、(1)でPtrXのリンク先をPtr2にして、(2)でPtr1のリンク先をPtrXに書き換えてやればよい。しかし、プロセサAがDataXを挿入しようとし、同時にプロセサBがDataYを同じ位置に挿入しようとしていると、一方の挿入は失敗してしまう。

図9.20 リスト構造への要素の挿入処理

セマフォ(札メモリ)を使って、このリスト構造へのアクセス権を制御しても良いが、この場合、まず、新しい要素を挿入するPtr1のリンク先アドレスを読み、挿入に必要な(1)の処理を行い、最後に再びPtr1を読んで、それが以前の値と一致している場合は他のプロセサが挿入を行っていないので、Ptr1のリンク先を挿入した要素のアドレスで置き換えるという操作をアトミックに行うことができれば、セマフォを使うより、ずっと効率よく処理を行うことができる。

このような操作を行うには、値がゼロかどうかを判定するTest and Set命令では不十分で、命令の第一オペランドの任意の値と比較を行い、一致した場合は、命令の第二オペランドの値をメモリに書き込むCompare and Swap(CAS)命令を設ける必要がある。

CAS命令を使う場合、まず、Ptr1を読み、(2)の処理を行ってから、CAS命令の第一オペランドに読んだPtr1の値、第二オペランドにPtrXのアドレスをセットして、Ptr1をアクセスする。最初の読み込みからCAS命令までの間に、別のプロセサが割り込んでPtr1を書き換えた場合は、二度目に読んだ値が一致しないので、その場合は、要素の追加は失敗である。

他のプロセサが割り込んでいない場合は、二度目に読んだポインタ値は一回目と同じであるので、挿入した要素へのポインタと置き換えられ、要素の追加が成功する。Test and Set命令は、札をひっくり返しクリティカルセクションを保護するのに用いられるが、このポインタの書き換えの例のように、処理によっては、CAS命令を使えば、特別にクリティカルセクションを作らなくても、複数のプロセサからアクセスされる構造をアトミックにアクセスすることができる。

以上述べたように、マルチプロセサで共用されるデータ構造に対しては、このような実質的にアトミックなメモリアクセスを行う命令が設けられており、これらの命令を使用することにより、安全に使用中の札をひっくり返すことができるようになっている。

NS、スマートな太陽電池パネルを実現するチップセットを発表

National Semiconductor(NS)は、太陽電池パネル内蔵型チップセット「SolarMagic SM3320」を発表、太陽光発電システムとして「スマート・パネル」というカテゴリを提唱した。

太陽光発電モジュールに制御回路として搭載することで、余分な場所をとらずに個々のバラつきを抑制し高い効率での発電を実現することが可能となる

従来の太陽電池パネルは経年劣化や日陰などよるミスマッチにより回収可能な発電力の低下が問題となっていたがスマート・パネルでは、SM3320をパネル内に組み込むことでこうしたミスマッチを回避し、太陽光発電システムの発電量回収効率の最大化を実現することができる。

同製品は、太陽光発電システムの発電量回収、信頼性、費用対効果の最適化を、パネル内蔵型電子技術という観点で開発されたアナログ半導体技術集約型パワーマネジメント・チップセット。太陽電池パネルの背面に位置する配線箱に直接、SolarMagicパワー・オプティマイザの動作内蔵を可能にするもので、ボードレベル・システムあるいはチップセットとして提供される。

独自開発による10個のアナログおよびミクスドシグナルICで構成されており、信頼性の高いデジタル制御とアナログ・センシング/シグナリングの組み合わせを実現している。また、独自開発のアルゴリズムは太陽光パネル単位の最大電力点追従(MPPT)方式を適用しており、モジュールからの入力電圧と電流を最適な出力電圧と電流の組み合わせに変換し、発電量回収を最適化することが可能だ。さらにセンシング技術を活用することで、入力電圧とアレイ側に流れる電流を検知、調整し、最適なストリング・レベルを実現している。

このほか効率99.5%を実現した高集積型350W 3モード・パワーコンバータを内蔵しており、これにより発電量回収を最大化するための個々のパネルの電圧の昇圧、パススルーまたは降圧を可能とする。また、オプションとして、防火のためのパネル・シャットオフ機能と安全メカニズムも用意されている。

なお、ボードレベル・システムはサイズが5インチ×3.5インチ×0.5インチ、重さが約6.4オンスで、太陽光発電パネルの配線箱に容易に組み込むことが可能だ。現在、ボードレベル・システムの配線箱とモジュールへの内蔵化がパートナー企業によって進められており、こうしたパートナー企業による製品発表が2010年内に複数行われる予定としている。