仕事で役立つ人気ビジネスアプリおすすめ!

[PR]

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

一歩進んだ電子工作をやってみよう (3) 回路図の入力をしてみる

そもそも回路図ってどんなもの?

そもそも回路図ってどんなもの?

この連載も3回目、今回は回路図を回路図CADである「CADLUS Circuit」を使って入力してみよう。

回路図というと難しく感じてしまう方もいるかもしれない。回路図なんか今まで書いたことないよ、という方もいることだろう。しかしよく思い出してほしい。小学校の頃乾電池で豆電球を光らせる回路を作ったとき、こんな図を描かなかっただろうか。

豆電球を光らせるための回路(左が電池、右が電球となる)

これも立派な回路図である。豆電球という部品から出ている2本の線(端子)を乾電池のどこにつなぐのかが明確に示されている。場合によってはこれにスイッチがついている場合もあっただろう。その場合はこうなる。

豆電球の回路図その2(真ん中上辺りにスイッチが付いた)

これも豆電球という部品の端子とスイッチという部品の端子と乾電池をどう接続するかが示されているわけだ。また乾電池や電球、スイッチは実物とはかけ離れた形の記号で表されていることにも注意しておきたい。これは回路記号と呼ばれ、実際の部品を抽象化したような形の記号がJIS(日本の場合)で規格化されている。

つまり回路図とは「部品のどことどこをつなぐかを過不足なく表した図」ということになる。規格化された回路記号を使ってつなぎ方の情報さえ載っていれば、あとはどう描いても構わない。とはいえ見にくい回路図をわざわざ描くこともないので、なるべくシンプルで分かりやすい回路図を描いていくことを心がけていこう。

ブレッドボードの回路にも回路図を使用

今回入力する回路は、この連載第1回でブレットボード上に載せたヘッドフォンアンプ回路だ。

この連載の第1回でも登場したブレッドボード上に載せた回路

いきなりこれを作ったわけではなく、元になった回路図がある。手描きで汚くて申し訳ないのだが、こんな感じだ。

ブレッドボードの回路を作るために書いた回路図(手書きのため見づらいところがあるのはご容赦願いたい)

実際は抵抗などの数値を試行錯誤したためもっと汚いのだが、それもどうかと思ったので清書してみた。上半分がヘッドフォンアンプ本体で、下半分は電源回路だ。ヘッドフォンアンプは面倒で1ch分しか描いていないが実際は左右2ch分作らなければならないことに注意しよう。

抵抗やコンデンサは良いとして、真ん中にある三角形の記号は今回のヘッドフォンアンプの肝になるオペアンプだ。今回は8ピンのDIPパッケージで2回路入りのものを採用することにした。このパッケージは一般的なので、気に入ったオペアンプを使うことが可能になるからだ。CADLUS CircuitではTL072という型番で登録されているものがそれにあたるので、利用することにしよう。

CADLUS Circuitを使ってみる

それでは実際にCADLUS Circuitを起動して回路図を描いてみることにする。

CADLUS Circuitを起動するとA4図面枠が呼び出されているが、今回は部品点数も少ないのでもっと小さな図面枠を使うことにしよう。ツールバーの左端にある「新規図面」ボタンか「ファイル」-「新規図面作成」を選び、「B5図面枠.drw」を選択する。すると先ほどよりも小さい図面枠が出てきたのではないかと思う。

新規図面作成で図面枠を選択

次に部品を部品ライブラリから呼び出す作業を行う。ツールバーの「部品配置」ボタンを押した後、図面の任意の位置を左クリックすると部品の選択ダイアログが開くので、必要な部品を選んでOKを押せば図面上にその部品が配置される。

部品配置ボタン(図面の任意の位置をクリックすると部品の選択ダイアログが開く)

部品の選択ダイアログ(この中から必要な部品を選んでOKで配置される)

今回使う部品はそれぞれ以下のライブラリの中に収録されているので、参考にしてもらいたい。

オペアンプ(TL072) → Analog抵抗 → Discreteコンデンサ → Discrete電解コンデンサ → Discrete無極性コンデンサ → Discreteコネクタ(電池の代わり) → ConswGND → Pwrsymヘッドフォン端子(ステレオミニジャック) → Consw

左右の音量を同時に変えられる2連ボリュームはシンボルがなかったので今回自作した。といっても難しいことはなく、すでにある部品パターンにちょっと属性を追加しただけで作ることができた。

今回はすでに回路の検証が済んでいることに加え、部品点数が少なく一般的な部品ばかりだったため、すべての部品を一度に図面に並べてみた。

すべての部品を並べたところ(これを並べ替えて線でつないで回路にする)

これを前に挙げた手描きの回路図と同じように並べ替えていき、さらに各部品を線でつなぐことにより回路としていくわけだ。

配線はツールバーの「配線」ボタンを使う。

配線ボタンで各部品の配線を行う

接点接続ボタンで配線同士の好転に接点をつけることができる

このボタンが押されている時は配線モードになっているので、あとは各部品の端子をつないでいけばよい。注意すべきは2点あり、まず配線同士の交点には「接点接続」ボタンを使って接点を付ける必要があることと、配線が部品の接点を横切ると接続したことと同じになってしまうということだ。どちらもCADLUS Circuitのマニュアルpdfに書かれているのでよく読んでおこう。

また、「配線」ボタンの左隣にある太い線のボタンはバスと言って複数の配線、例えばアドレスやデータといったものをまとめて表現するために使うものだ。右隣の黄色い線と破線は配線ではなく単なる図形の線で、図面を分かりやすくするために使う。その右隣が「接点接続」ボタンで、さらに右隣にある斜めの線のボタン2種類はバスからバスや配線を取り出す時に使う専用の線だ。今回は使わなかったがマイコンの回路設計を行う時などは使うことになるだろう。

さて、そうやってできあがったのがこの回路図だ。

部品を配置し、各部品を配線した回路図

部品を並べた時には部品の参照名(R1,C1など)が同じになってしまっていたが、きちんとふり直した。下にあるのが電源回路だが、その右端にあるのはオペアンプの電源シンボルだ。これはTL072とは別にDiscreteライブラリに「VCC_DOPAMP」という名前で入っているものを配置して部品名をTL072、参照名をU1に直したものだ。

回路図の入力が完了したら、回路図データチェックを行っておこう。「ファイル」-「回路図データチェック」を選択して「はい」を選ぶだけだ。これで未結線の部品があった場合は表示してくれる。

データチェックでエラーがあればそれを教えてくれる

間違えて結線してしまっているなどの場合はエラーとして出てこないので、これでOKだからといって全て大丈夫という訳ではないのだが、1つの目安にはなるだろう。

ここまでできれば回路図は完成だ。次はついに基板CADであるCADLUS Xを使ってプリント基板の設計を行うので、楽しみにしていてほしい。

インフロー

インフローはプリント基板ネット通販「P板.com(ピーバンドットコム)」を運営しており、プリント基板設計、製造、実装、メタルマスク販売をサイト上で完結するサービスとして提供し、試作から量産に関わる、リジット基板からフレキシブル基板までニーズに対応できる幅広いサービスを提供しています。同サイトは、国内約6,000社との取引実績、約1万4,000名のユーザー登録を持ちます。また、電気・電子エンジニア向けSNS「@ele(アットマークエレ)」を運営しています。回路図データベース構築を目的とした、電気・電子エンジニア向けのSNSで、会員数約1,600名となっています。

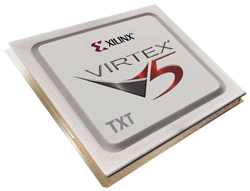

Xilinx、Virtex-5ファミリに新プラットフォームを追加

Xilinxは23日(米国時間)、通信機器メーカー向けFPGAソリューションとして、Virtex-5ファミリの新プラットフォーム「Virtex-5 TXT」を発表した。ロジックセル数が14万8,480の「XC5VTX150T」と同23万9,616の「XC5VTX240T」の2製品が用意されており、いずれもサンプル出荷は2008年末までに開始され、2009年第1四半期から量産出荷が行われる予定である。なお、単価はXC5VTX150Tで、2009年下半期で5,000個購入した場合500ドル以下に設定される見込み。

Virtex-5 TXTプラットフォームの外観イメージ

同プラットフォームは、48個の6.5Gbpsトランシーバを持ち、100GbEアプリケーションのために最適化されたもの。設計においては、10/100Gbps リンクの高信頼度な動作のためのシグナルインテグリティの改善、チャネルあたりの消費電力の低減、およびマルチプルプロトコルをサポートするためのプログラム機能などが考慮されており、100Gbps光モジュールとメディア・アクセス・コントローラ (MAC) 間のインタフェースにおける新しいスタンダードに適応可能なように設計されている。

また、100GbE~120Gbps Interlaken、40Gbps Quad XAUI~50Gbps Interlaken、OC-768~OTU-3、SFI-5~4xSFI4.2といったネットワークブリッジを構築するために必要なシリアルI/Oの総合バンド幅600Gbpsを提供することが可能である。

このほか、他のVirtex-5プラットフォームと同様に、ASMBLアーキテクチャの採用のほか、「ExpressFabricロジックアーキテクチャ」、高速メモリに外部バッファを作成するための1.25Gbps SelectIOテクノロジ、「Virtex-5 FXTプラットフォーム」で導入されたGXTトランシーバなどが用いられている。

コンピュータアーキテクチャの話 (129) 実行資源の予約

会議室であるが、最近ではイントラネット上のグループウェアで予約管理が行われるというような方法も一般化しているが、昔は、会議室の入り口に予約表がぶら下がっていて、既に予約が書き込まれていなければ、そこに使用時間帯と使用者の名前を書き込んで予約するという方法が普通であった。

パイプラインの資源に対しても同じ手法で、メモリや演算器などの各資源ごとに予約表を作って、命令のデコードサイクルに、その命令の実行を完了するまでの全てのサイクルで必要な資源の予約表をチェックし、全ての資源が予約可能であれば、それらの資源の使用を予約表に書き込んで実行に入る。一方、どれかの資源が予約できない場合は命令の実行開始をストールする。

予約表であるが、図4.7のようにシフトレジスタで構成するのが便利である。

図4.7:予約表の構造

FF1は、次のサイクルでのこの資源の予約状況を記録し、FF2は、2サイクル後の資源の予約状況を記録する。FF3、FF4は更にその先のサイクルの予約状況を記録するFFである。命令をデコードすると、その命令の種別が分かり、それ以降の各サイクルで、どの資源を必要とするかが分かる。従って、それぞれの資源の予約表に対して、それを必要とするサイクル数を図4.7のCycleに入力すると、次のサイクルで必要とする場合はFF1、その更に次のサイクルで必要な場合はFF2、…の状態が選択されてReserved出力に出てくる。これが”1″であれば、先行する実行中の命令でその資源が予約されているので、その命令の実行はストールすることになる。一方、”0″であれば予約の無い状態であるので、図の上側のデコーダを通して対応するFFに”1″をセットして予約を行う。

そして、1サイクルが終わると、予約表のFF2をFF1、FF3をFF2、FF4をFF3にコピーしてシフトを行い、FF4には”0″を入れる。このようにシフトを行うことにより、次の命令(実行をストールした場合は、同じ命令であるが)のデコードと資源予約を行う状態とする。

図4.7には一つの資源の予約表しか書いてないが、各資源に同様な予約表があり、その命令の実行で必要となる全ての資源の予約表をチェックして、全ての資源が予約でき、必要なオペランドもバリッドであることを確認してから、その命令の実行を開始する。そして、これらの条件の一つでも欠けている場合には、その命令の実行を開始せず、次のサイクルに再度、オペランドや資源のチェックを行う。このようにして命令の実行を開始すれば、パイプラインでの命令の実行途中で必要な資源が使えないという事態は起こらない。

なお、デコードステージで条件が欠けていて命令の実行をストールする場合は、メモリから読み出された次の命令を命令レジスタに書き込まないようにすれば良い。こうしておけば、次のサイクルにも同じ命令がデコードされ、再度、実行に必要なオペランドや資源のチェックが行われることになる。また、同時にプログラムカウンタの更新を抑止しておけば、その次の命令フェッチのアドレスも同じであり、ストール中は、命令デコードまでの部分は同じ動作が繰り返されることになり矛盾は生じない。

ロームと本田技術研究所、SiCによるハイパワーインバータモジュールを開発

ロームと本田技術研究所は、SiC-SBDならびにSiC-MOSFETを搭載した1200V/230A(280kVA相当)クラスの次世代電気動力車向けハイパワーインバータモジュールを開発したことを発表した。ロームのSiCデバイス技術と本田技術研究所のハイパワーモジュール技術を融合させることにより、フルSiCデバイスによるハイパワーインバータモジュールを実現したという。

ロームと本田技術研究所が共同で開発したSiCハイパワーインバータモジュール

同インバータモジュールは、コンバータ回路(1相)とインバータ回路(3相)を1パッケージに搭載することで、小型化を実現している。

また、ロームの開発によるSiCデバイスの素子単体特性は、Si-IGBTと比較してスイッチング損失が約1/7となっており、パワーモジュールとしての性能もスイッチング損失が従来のSiデバイスと比較して約1/4以下に低減できることが確認されたという。これにより、オン損失を含めた電力交換時の総損失の低減が可能となったほか、スイッチング損失が低減した分、駆動周波数を引き上げることが可能となり、例えばSi-IGBTを使用した場合のPWM周波数20kHzに対し、4倍となる80kHzへと向上させることが可能となるという。

インバータへの応用では、低損失低減を目的に使用する場合、発熱量が抑えられるため、冷却機器の小型化や温度マネージメントの設計範囲の拡大などに効果が期待できるとしている。また、昇圧コンバータ応用では、従来に対し4倍駆動周波数を高くできるため、周辺部品の小型化、軽量化により機器としての出力容積密度の向上を図ることが可能になるという。

今回開発されたモジュールをハイブリッド車(HEV)や電気自動車(EV)に適用することで、損失の低減、システムの小型・軽量化が期待できるが、両社は今後、SiC-MOSFETの単体性能をさらに引き出すパワーモジュール構造の改善ならびに、SiC-MOSFETの微細化や構造の改良による性能の向上を目指すとしている。

IDT、Silicon Optixの資産買収に関する説明会を開催

半導体ベンダの米Integrated Device Technology(IDT)は10月28日、10月21日に行ったファブレスベンダである米SiliconOptixのビデオプロセッシング技術「HQV(Hollywood Quality Video)」ならびに関連資産の買収についての説明会を開催した。

同買収に伴い、IDTはSilicon OptixのHQVデバイスラインナップ「Reon」のほか、IPおよびエンジニアリングチームを傘下に加えることとなる。

HQV技術は、1080iから1080pへのHDインタレース解除機能(デインタレース)や、ブロックノイズを除去する多方向角型フィルタなどの機能を用いることで、高品質のHD映像を実現する。また、各種ノイズを除去するフィルタなどの機能を用いることで、SDの画質をHDの品質に近づけることが可能であり、アナログTVの高画質化などもできる。

デインタレース機能やブロックノイズの除去機能などを搭載している

DT Vice President:Strategic Planning & Worldwide MarketingのChad Taggard氏

IDTでは、「当面はReonの販売を行うが、将来的にはタイミングコントローラ(TCON)やDisplay Port製品との統合も検討していく」(IDT Vice President:Strategic Planning & Worldwide MarketingのChad Taggard氏)とするが、具体的には「まだ買収したばかりで、どのような製品展開を行うかも決まっていない」(同)とした。

また、IPとして他社へ提供する意思は今のところ無く、自社製品として展開していくという。製造はファウンドリを活用。プロセスは130nmもしくは90nmとしている。

ディスプレイ市場全体としては、2009年中ごろに伝送帯域を5.4Gbpsまで拡張したDisplay Port バージョン1.2の規格化作業が終了する予定であるとしたほか、同年のノートPCの出荷台数が1億3,000万台、モニタが1億8,500万台、LCD-TVが1億1,200万台との予測を提示、こうした市場に向けて、「Silicon Optixで培われた技術力とIDTのインフラを活用することで、市場での躍進を狙う」(同)とした。

IDTのDisplay Port製品群のロードマップ

なお、同社では、今後FPDのシステムの一部がパネル側にシステムとして搭載されると見込んでおり、パネルメーカーが存在する日本市場は重要な市場と見ている。そのため、そうしたパネルメーカーなどへの拡販などを行うことで少なくとも売り上げの倍増を図っていきたいとした。