仕事で役立つ人気ビジネスアプリおすすめ!

[PR]

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

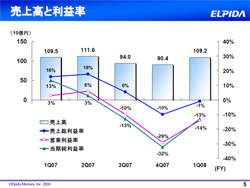

エルピーダの2009年3月期第1四半期業績、3四半期連続で赤字を計上

エルピーダメモリは7日、2009円3月期第四半期(4-6月)の決算概要を発表した。売上高は前年同期比0.2%減の1,092億2,700万円、営業損益は前年同期は37億4,300万円の黒字から156億2,200万円の損失、経常損益は同37億3,600万円の黒字から154億600万円の損失、純損益は同145億5,400万円の黒字から137億6,900万円の損失となり、3四半期連続の赤字となった。

エルピーダメモリの売上高と利益率の推移

分野別売上高構成比は、モバイル機器やデジタル家電向けのプレミアDRAMが42%、PC、サーバ向けのコンピューティングDRAMが58%となり、前四半期と比べ7ポイントほどコンピューティングDRAMの比率が高まった。台湾Powerchip Semiconductor(PSC)との合弁会社Rexchip Electronicsの売上高が全体に占める割合は10%程度、それ以外の委託先生産分売上高比率は18%となった。なお、プレミアDRAMは、比率は下がっているものの、売り上げとしては前四半期とほぼ同等であるとしている。

分野別の売上高構成比

前四半期比ビット成長率(出荷数量の増減率)は、期初予測の15~20%を超え、26%となった。これに伴い、同社では、通期の同ビット成長率を期初の70%から80~90%へと引き上げるとともに、プロセスの微細化をより進めるために設備投資額およびRexchipへの出資額を1,000億円から1,200億円へと引き上げた。主なものとしては、広島の300mmウェハ対応Fab「E300」の65nmプロセス向け投資を増額したほか、Rexchipへの出資として2009年3月期第4四半期(2009年1-3月)に約200億円行うことを予定している。

同社取締役兼Co-CTOの安達隆郎氏は、DRAM市場の成長率と前年同期比ビット成長率の動きに対し「ビット成長率が50%をきると市場成長率が高まるのが過去の例。現在の状況もこれと似通っており、マクロ経済的にはDRAM市場は不況を脱し、成長局面に入る可能性が出てきた」とし、今後、市場が高い成長を示す可能性があることを示した。

ビット成長率とDRAM市場の成長率

ポジティブな要因としては、クリスマスおよび正月というイベントが控える年末に向けてDRAMが需要期に入ったこと、ならびに2008年下期におけるPCのDRAM搭載量が、伸び率が低下するものの引き続き成長が期待できること、DRAMメーカー各社の設備投資のカットと200mmウェハ対応ファブにおけるDRAM生産量の減少などを挙げた。ただし、リスク要因として、世界的な景気の減速によるPCおよびハイエンド携帯電話の需要が減退する可能性があるとし、不透明感は強くあるとした。

同社では2008年1月より65nmプロセスでのDRAMの生産を開始、現在の月産1万枚規模の生産能力を年末までに月産3万6,000枚に引き上げることを計画している。また、同年9月からは50nmプロセスを採用したDDR3ならびにモバイルRAMのサンプル品の出荷を、2009年第1四半期中に量産をそれぞれ開始することを予定している。50nmプロセスでは、新規にArF液浸リソグラフィを採用するほか、Cu配線プロセスを本格的に導入するが、「液浸やCuの導入でコンタミネーションの発生などを危惧していたが、そういった問題も発生しておらず、スムーズな立ち上がりを見せている」(同)としており、今後は歩留まりの向上などを中心に取り組みを進めていくとした。

このほか、装置の売却を行った広島の200mmウェハ対応Fab「E200」では、現在、TSV(Through Silicon Via)のラインを設置中としており、2009年中に量産技術の確立を行い、2010年に量産を開始する計画であるという。

NECエレ、半導体ものづくり推進センターによる保全技能者の育成を強化

NECエレクトロニクスは25日、同社相模原事業所に2007年11月15日に設置した「半導体ものづくり推進センター」における海外からの研修生の受け入れ人数を2008年度下期で2008年度上期比で30%程度増員し、40名程度受け入れることを決定した。また、それに併せて同センターの詳細を報道陣に披露した。

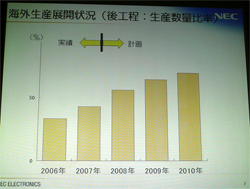

背景は海外生産の推進

同センターの設立の背景には、同社が2007年2月に発表した再生プランがある。同プランを確実に遂行するためには、海外工場における生産拡大に伴う人材の増強および指導者の早期育成がコスト面でも品質の面でも欠かせなかったという。この海外シフトは中国の首鋼日電電子(SGNEC)およびマレーシアのNEC Semiconductors Malaysia(NECSEM<)を中心に行われており、後工程における海外生産の展開状況は2007年度では50%以下だが、2008年度で50%を突破し、今後も増え続けていく計画だ。

後工程の海外生産展開状況の推移

NECエレクトロニクス 生産本部 半導体ものづくり推進センター センター長 中嶋正博氏

同社 生産本部 半導体ものづくり推進センター センター長 中嶋正博氏は、「海外工場の競争力を上げるためには、次代の幹部候補の育成まで含めて国内並みの人材育成を行う必要がある。半導体ものづくり推進センターはそのために設立された組織」としており、同センターを中心とした海外現地法人に対する支援を行っていくことを強調した。

現在同センターでは、高い技術レベルと実践力を兼ね備えた後工程装置の保全トレーナの育成、保全業務に必要な知識を教えられる講師であるテクニカル講師の育成が行われており、将来的には管理監督者の育成も行っていくことが予定されている。

いずれの育成についても、加工技術や組み立て技術といった伝承すべき技能・ノウハウに対し、インダストリアルエンジニア(IE)による作業の分析、ノウハウの調査が行われ、標準化(ベストプラクティス)やビデオによる説明化(見える化)などを基にカリキュラムなどを作成、技術の定着に向けて使用されている。

伝承すべき技能やノウハウを科学的な手法により見える化し、形式知化する

育成期間は2カ月以上

トレーナの育成は、基本は同社が定める4段階のスキルレベルの内、レベル2の人を対象に相模原事業所での基礎的な部分の教育を1カ月行い、その後国内の工場に出向きOJTを1カ月行うことで、スキルレベルを4まで引き上げようというもの。

トレーナ育成教育の概要

育成もこの2カ月で終了というわけではなく、6カ月後にフォローアップを入れるなど、アフターケアも行っている。「通常、装置メーカーで行われる教育は1週間程度と短い。そのため、応用的なメンテナンスなどが難しかったのが現状。2カ月にわたり教育を行うことで、場面場面で異なる対応ができる人材が育成できるようになった」(同)とする。

スキル評価による技能水準の把握(レベルは1~4まであり、レベル3に達して1人前とのこと)

テクニカル講師の育成は、同社の標準カリキュラムの教育を海外工場で教えることができる講師を育成することが目的。そのため、教育期間は6カ月と長めとなっている。「6カ月を一気に行うことは非常に難しいのが現状。そのため、期間を分割して行っている」(同)というのが実情だという。

テクニカル講師育成の概要

後工程に関する基礎から応用まですべてを集約

同社相模原事業所内に設置された同センターのトレーニングルームの広さは400平米。ここに2つの教室が用意されさまざまな授業が行われるほか、複数のトレーニングユニットや各工場などから持ち込まれた生産設備などが配備され、それを用いた学習なども行われる。

トレーニングルームのレイアウト

教室での講義風景(同ルームの公開時は海外研修生を対象にアナログ電子回路に関する講義が行われていた)

トレーニングユニットは、実践に役立つ教育教材ということで、自社開発されたものが用いられている。主なものとしては、ネジの締め付け強度を測るためのユニットや故意に回路やセンサ、リレーなどを不具合の状態をすることで、状態を確認するためのユニット、電気やメカ・エアーの複合回路をいかに調整するかを学ぶユニットなどがある。

トレーニングルームに置かれたユニット各種(左が複合調整ユニット、右が保全実務ユニット)

また、装置に関しては後工程ということで主にボールボンダやワイヤボンダ、ダイボンダなどが8種13台用意されているが、これには装置メーカーからのレンタルも含まれており、「時期を見て入れ替えも行っており、すでに新たに借り入れる装置についても決定済み」(同)とのこと。

後工程用の装置がずらり並ぶ(この他にもロジックテスタなどが置かれている)

装置の傍らには不具合要因などを表すパネルなどが置かれている

このほか、ビデオによる学習もトレーニングルームで行われる。これも単に作業を映して流すだけではなく、上部に作業のタイトル、下部に作業手順を表示、数値などを具体的に表示するなどの工夫が施されている。対応言語は日本語のほか英語が用意されており、今後中国語についても対応を検討していくとしている。

実際にビデオを見て手順を確認する

数値なども表示することにより目安を分かりやすくしている

なお、同社ではこうしたトレーニングルームをSGNECやNECSEMにも設置するよう準備を進めている。すでにSGNECについては2008年5月に開設しており、レベル3以上のトレーナの養成に向けた教育が開始されている。一方のNECSEMには2009年4月にトレーニングルームを開設する予定としている。

NANDアレイ採用のORNAND2で組み込み市場を狙うSpansion

Spansionは26日、都内で記者会見を開き、同社が2007年11月に初めて発表し、2008年8月にSemiconductor Manufacturing International(SMIC)に生産委託を行うことを発表した同社のNAND型フラッシュメモリ「MirrorBit ORNAND2」に関する説明を行った。

独自技術であるMirrorBit

Spansion セキュリティ&先端技術事業部門 エグゼクティブ・バイスプレジデント Carla Golla氏

同社は独自のチャージトラッピング技術である「MirrorBit」をフラッシュメモリに適用している。同技術は、本来メモリセルの両側に物理的に異なる2つの電荷をそれぞれ記憶させることで、フラッシュメモリアレイの本来の容量を2倍にする技術であったが、最近同社では、MirrorBit型の構造そのものをMirrorBitと称しているようだ。

そのため、同社ではMirrorBitを中心に据え、NORやNANDの技術をそこに組み込む手法を取り入れている。同社セキュリティ&先端技術事業部門(SATD:Security and Advanced Technology Division)エグゼクティブ・バイスプレジデントのCarla Golla氏は、「異なったセルをベースにしたフラッシュメモリを出すことで、さまざまなアーキテクチャに対応することができる」とその特徴を語る。

MirrorBitの技術はNOR、NAND双方に適用できる

MirrorBitとNANDを組み合わせ

ORNAND2はMirrorBitとNANDの技術を組み合わせたもので、第1世代は43nmプロセスでの製造が予定されている。NANDアレイに接続した独自のSONOSベースのセル構造を採用、周辺回路を小さくすることができるためセルサイズは4.0λ2で済むという。また、MirrorBitを採用しているため、SLCとMLC双方に対応できるのも特長だ。とは言え、同社としてはMLCに比べビット容量は減るものの信頼性や耐久性、性能などの面で優位であるSLCを基本的に採用するという。そのためMirrorBitと言えどもチャージしている電荷は1つとなっている。

MirrorBit ORNAND2テクノロジの特長

これは同社が同製品で狙う市場と戦略に起因している。同社としては「ORNAND2は特定の市場で活用されることを期待している」(同)としており、その主なターゲットとしては携帯電話、デジタル家電といった分野の組み込み用途であるという。そのため、容量も1~4Gビットまでに抑えるとし、多くても8Gビット程度であり「組込機器で求められる最適な容量を狙っていきたい」(同)という。

同容量帯の組込機器向けにはすでにMirrorBitとNORを組み合わせた「ORNAND1」があるが、時期を見て主力はORNAND2に移行していくはずだという。ただし、NORを用いたORNAND1はNANDで必ず発生するバッドブロックの影響が少ないため、クリティカルな領域などに向けて引き続き提供していく計画であるという。

ORNAND2による差別化技術

また、SpansionではORNAND2を用いた差別化技術の開発も行っている。主なものとしては従来はアプリケーションチップセットやプロセッサに組み込まれるか、個別に必要であったコントローラをNAND側に組み込んだ「Managed NAND」がある。これにより、コントローラおよびインタフェースの機能を統合することが可能となり、差別化を図ることが可能になるという。

Managed NANDの概要

ORNAND2の生産はSMICのみを計画

ORNADN2は43nmプロセスを用いて2009年中の生産開始が予定されている。同社の計画では、自社の工場で同製品の製造は行わず、委託先のSMICのみで製造を行う計画としている。これは43nmプロセスのみに限った話ではなく、32nm以降の微細プロセスでも同様の計画のようだ。その32nmプロセス以降の状況だが、現在、Spansionの300mmウェハに対応した研究施設「Submicron Development Center(SDC)」において、32nmプロセスがR&D段階、22nmプロセスがリサーチの段階にあるという。

MirrorBit ORNAND2のプロセス開発状況

席を離れると自動的に省電力モードに

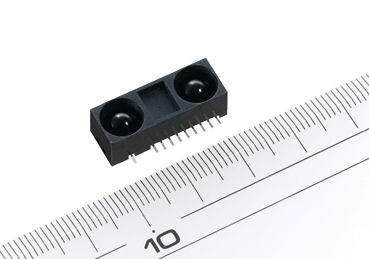

シャープは、温水洗浄便座や手を検知して温風を送るエアータオルなど、サニタリー機器に広く搭載されている測距センサを小型し、9月30日からサンプル出荷すると発表した。

シャープが開発した測距センサ(GP2Y0A60SZ0F)は、22.0×8.0×7.2ミリメートルと、従来製品の約6分の1となる小型化を実現。検知距離は1.5メートルだ。このセンサをパソコンやディスプレイなどのOA機器に搭載することにより、離席時に自動的にスリープモードに入るといった省エネ機能を実現できるという。

シャープが開発した測距センサ(GP2Y0A60SZ0F)

小型化は、同社が長年培ってきた光学設計技術を駆使し、レンズと受光素子の小型化と双方の間隔を短縮したほか、抵抗やコンデンサなどを取りこんだICの新規開発などにより実現した。

9月30日からサンプル出荷を開始し、サンプル価格は税込みで450円。11月からは月産10万台の量産体制に入る予定だ。

Cypress、不揮発性SRAM搭載8ビットマイコンを製品化

半導体ベンダの米Cypress Semiconductorは、同社の不揮発性SRAM「nvSRAM」とデジタル・アナログ混合8ビットマイコン「PSoC(Programmable System-on-Chip)」を1チップ上に統合した製品「PSoC NVファミリ」を発表した。3.3V品となる「CY8CN102B」がサンプル出荷中で、2008年第4四半期中の量産開始を予定している。

PSoCとnvSRAMを1チップ化した8ビットマイコン「PSoC NV」

従来のSRAMは電源が落ちるとデータは消えてしまうという欠点があった。nvSRAMは、SRAMの周囲にSONOS型の不揮発性メモリ(NVM:Non Volatile Vemory)を置く事で、電力低下時などのイベントでSRAMのデータをNVMに退避させ、データの消失を防ぐというもの。NVMの書き換え回数は20万回、データ保持期間は20年という。

日本サイプレス 本部長 マーケティング・応用技術の吉澤仁氏

PSoC NVは、従来のPSoCの機能はそのままに、新たにnvSRAMの機能を加えたもの。同社日本法人の本部長 マーケティング・応用技術の吉澤仁氏は、「MRAMやFeRAMなどの新たなメモリが登場してきているが、まだ信頼性の面などで不安がある。また速度についてもSRAMの方がまだ早い。nvSRAMはそうした意味での次世代に向けた解決策の1つとなる」とし、PSoC NVの製品化については「PSoCとnvSRAMを集積することに対しての要求が高かったため」とした。

現在、サンプル品として提供されているPSoC NVはPSoCとnvSRAMをスタックパッケージにより1チップ化したものだが、「2009年第1四半期にはシングルダイに集積した製品を第2世代品として提供できる計画」(同)としており、その際はプロセスのシュリンクによりチップサイズの肥大化を抑えるとしている。

PSoC NVに搭載されるnvSRAMの容量は64K/128K/256KBの3種類。現在はチップがスタックされているためPSoCのコア側としてはGPIO(General Purpose I/O)により管理するという形をとっているが、シングルダイ化により直接バス経由による制御に移行するようだ。

nvSRAMのほか、プログラム格納用の32KBのフラッシュメモリならびにプログラム実行用の2KBのSRAMを搭載している。その他の機能としては、24MHz動作のM8Cプロセッサ、12個のアナログブロック(8~14ビットまで選択可能なA/Dコンバータ、6~9ビットまで選択可能なD/Aコンバータなどに利用)、16個のデジタルブロック(8~32ビットのタイマ、カウンタ、PWMなどのほか、UARTなどに利用)などを内蔵している。

PSoC NVのブロックダイアグラム(緑の部分、上から3段目にnvSRAMが加わった。ちなみに「DIGITAL BLOCKS」と「ANALOG BLOCKS」を書き換えることで、仕様の変更が可能な点が通常のマイコンとは違うところとなっている)

同社では、「技術トレンドが読めなくなった現在では、出荷ギリギリまで仕様が定まりきらなかったり、より多くのデータを保持することによる解析の強化、データ量の増加を実現するためのセンサなどの微弱信号の増幅のための回路増によるコスト増などの課題があった」(同)とし、いつでもハードウェアの仕様変更が可能で、アナログ機能も持つPSoCと、書き換え回数が多く、データ格納量も多いnvSRAMを組み合わせた同製品は、従来、PSoCが活用されていた主な分野である民生機器以外のサーバや産業機器などの分野でも「グリーン化が求められる現在、細かく電源を制御することが求められており、そういった意味ではアナログの機能まで含んでいるPSoC NVが意味を持つようになり、システムの1部ないし全部の置き換えを狙える」(同)とする。

また、ソフトウェアのサポートとしてはPSoC用の統合開発環境「PSoC Designer」がPSoC NVに対応。基本機能として、nvSRAMに対するリード/ライト機能が追加されたほか、将来的にはどのようにSRAMにデータを書き込むのかというようなデータストラクチャ的な機能の追加も予定されている。

さらに、複数のアナログチャネルからデータのサンプリングとロギングを行うことが可能で、電源障害時に多機能GUIを使い、プラグアンドプレイインタフェースを通じてデータを取り出し、システム障害が発生する前のイベントを再構築することができる「PSoC NV Demonstration Kit」の提供を2008年10月より、PSoC NVデバイスの混合シグナルおよびデータロギング機能を実験するためのプラットフォーム「PSoC NV Evalution Kit」の提供を2008年11月より同社のオンラインストアで開始する。PSoC NV Evalution Kitには、温度センシングとファン制御アプリケーションのためのファンモジュール、PSoC Designerおよびサンプルプロジェクトが含まれている。

なお、現在、3.3V品がサンプル出荷中であるが、同社では5V品「CY8CNP102E」の開発も行っているとしている。