仕事で役立つ人気ビジネスアプリおすすめ!

[PR]

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

コンピュータアーキテクチャの話 (56) 4ビットプロセサのアーキテクチャ設計

これまでは、ブロックダイヤグラムと命令セットの定義ありきから、Faggin氏の論理設計を追体験してきたが、この元となるブロックダイヤと命令セットをHoff氏はどのようにして作ったのであろうか?

Hoff氏が4004のマイクロアーキテクチャを考えた1969年頃の状況を見ると、今でも使われているメインフレームの最初のモデルグループであるIBM System/360が出来たのが1964年、そして、IBM 1130という16ビットのエンジニアリング向けのコンピュータも1965年に発売され、広く使用された。そして、ミニコンという名前で一世を風靡した12ビットのDEC社のPDP-8も1965年に発売されている。という状況で、これらのプロセサのアーキテクチャを参考にすることが出来た筈である。

4ビットプロセサのアーキテクチャを考えるにあたり、先ず、これらのマシンがどのような命令アーキテクチャを持っていたかを概観してみよう。

IBM Syetem/360

IBMのSystem/360は32ビットの本格的コンピュータで、当初のアーキテクチャから機能増強は続けられているものの、40年余りにわたって使い続けられているGene Amdahl博士の設計による傑作コンピュータアーキテクチャである。それまでは、コンピュータの命令セットはマシンごとに新たに作られていたが、超大型から小型メインフレームまでの一連のラインアップで全く同じ命令が動作するという点で画期的なマシンであった。但し、超大型は全ての命令をハードウェアが直接実行するのに対して、小さなモデルでは複雑な命令はマイクロプログラムを使用してエミュレートすることにより、小さなハードウェアで同じ命令セットの実行を可能とし、性能とコストのバリエーションを作り出していた。

IBM S/360は16個の汎用整数レジスタと4個の浮動小数点レジスタを持つアーキテクチャで、レジスタとレジスタの間で演算を行うRR形式の命令は16ビット長、レジスタとメモリ間で演算を行うRX形式の命令は32ビット長であった。この他にRS命令、SI命令、SS命令などがあったが、ここでは説明は省略する。

すべての命令は、命令の種別を示す8ビットのOPフィールドを持ち、その最初の2ビットは次のようなエンコードで命令の形式をあらわしている。

00:16ビット長 RR形式01:32ビット長 RX形式10:32ビット長 RS、またはSI形式11:48ビット長 SS形式

RR形式は、命令種別を表すOPが8ビット、レジスタを指定するR1とR2は、汎用レジスタの数が16個であるので、それぞれ4ビットである。

RR形式の命令は、たとえばOPが加算を行うADDの場合は、R1の汎用レジスタの内容とR2の汎用レジスタの内容を加算して、結果をR1に格納する。このように、2つのオペランドを同時に指定することが出来るので、S/360の命令は2アドレスの命令と呼ばれる。

RX形式は、次のような形であり、OPとR1はRR形式と同じであるが、その次は4ビットのX1、そして次の4ビットがB2、残りの12ビットがD2となっている。

RR形式はレジスタ間の演算しか指定できないが、RX形式では2番目のオペランドはメモリ上にあり、そのアドレスをX1、B2、D2で指定する。X1とB2はそれぞれ4ビットであり、汎用レジスタの番号を指定する。そしてD2は12ビットの値である。X1はインデックスレジスタ、B2はベースレジスタと呼ばれ、2番目のオペランドのメモリアドレスは、X1で指された汎用レジスタの内容とB2で指された汎用レジスタの内容とD2フィールドの12ビットの正の整数の合計で指定される。

S/360は大型メインフレームであり、タイムシェアリングで多数のプログラムを同時(ミクロには短い時間で実行するプログラムを切り替えるが、人間から見ると、同時並行的に複数のプログラムが実行されているように見える)に実行するという使い方を意識しており、メモリが高価であったので、複数のプログラムをメモリに詰め込んで格納するために、メモリアドレスを変更しても動かせるというリロケーション機能が必要であった。これを可能にするのがベースレジスタであり、このベースレジスタの内容を変えることにより、プログラムを格納する物理番地を変えることが出来るようになっている。そして、インデックスレジスタは命令自体を変更することなく、このレジスタの内容を変更するだけで文字列や配列の各要素をアクセスすることを可能としている。

ということで、RX形式の命令は、強力なメモリアドレッシング機能を持ち、このメモリアドレスの内容とR1レジスタの内容を演算してR1レジスタに格納する。また、OPがストア命令の場合は、R1レジスタの内容をX1、B2、D2で指定されるメモリアドレスに格納する。

System/360は語長が32ビットのマシンであるが、半分の16ビットのHalf Word、2倍の64ビットのDouble Wordのデータも扱える。また、ここでは説明を省いたSS形式などでは2進化10進数なども扱うことが出来る。

S/360の命令の特徴は、例えば、ADD命令はRR形式にもRX形式にも存在し、また、ハーフワード、ワード、ダブルワードというデータ形式が扱えるADD命令が揃っているというように、命令の種別と扱えるアドレッシング、データ形式の独立性が高い点で、コンピュータアーキテクチャでは、これを直交性が高い命令アーキテクチャと呼び、綺麗なアーキテクチャと見なしている。

例えば、コンパイラで加算を処理しようとするとき、最初はレジスタとメモリの加算であったものが、最適化を行っていくと、メモリを読まなくてもレジスタに置けるようになるというケースがある。直交性が高い命令なら単にRX形式の命令をRR形式の命令に置き換えれば良いが、対応するRR形式の命令が無ければ、異なる命令列が必要となりコスト計算が変わってくるというように、直交性の悪い命令体系だとコンパイラの処理が複雑になる。

コンピュータアーキテクチャの話 (16) キャッシュの構造や働き(応用編)

キャッシュに頻繁に使うデータを溜め、遅いメモリまでアクセスに行かないで済むようになれば性能が上がるのは当然であるが、それではどのくらい性能が上がるのであろうか?

プロセサの性能はクロック周波数まで考慮にいれた毎秒何命令実行できるかを示すMIPS(Million Instructions Per Second)のような絶対性能の指標もあるが、アーキテクチャ的な性能を言う時には、クロックの影響を除いて1サイクルに何命令実行できるかというIPC(Instructions Per Cycle)あるいは、その逆数である1命令の実行に何サイクルかかるかというCPI(Cycles Per Instruction)が使われる。

プログラムの実行のためのメモリアクセスの頻度は、当然、アプリケーション依存であるが、Load命令は5命令に1回、Store命令は10命令に1回、命令のフェッチは4バイト命令を64バイト単位でメモリからキャッシュに読み込むとすると、最低でも16命令に1回、平均的に半分として8命令に1回というのが、当たらずとも遠からずという頻度である。理想的な完全ヒットの1次キャッシュがあり、メモリアクセスの待ち時間が生じない場合のCPIをCcoreとし、上記の頻度でアクセス時間Tmのメモリをアクセスする場合のCPIは次の式で表わされる。

CPI=Ccore+Tm*(1/5+1/10+1/8)=Ccore+0.425Tm

Ccoreは最近のスーパースカラプロセサでは0.7~1サイクル/命令程度の値である。一方、プロセサのサイクルタイム(クロック周波数の逆数)は2.5GHzクロックの場合で0.4nsであり、メモリのアクセス時間が80nsとするとプロセサにとっては200サイクルであり、0.425Tmは85サイクルになる。つまり、平均命令実行時間は約86サイクルであり、そのうちの85サイクル分はメモリアクセス待ちという状態になる。これではプロセサコアにトランジスタを注ぎ込んで高度な並列実行をやらせてCcoreを改善しても、全く意味がない。

次に1次キャッシュを設けた場合は、命令当たりの1次キャッシュのミス率をm1、1次キャッシュをミスしてメモリからデータを取ってくる場合のアクセス時間をTmとすると、CPIは次式で表わされる。

CPI=Ccore+Tm*m1

1次キャッシュのミス率は実行するプログラムとキャッシュ量や構成によるが、32KB程度の1次キャッシュの場合、5~10%というのは当たらずとも遠からずの値であり、仮に10%とすると、Ccoreが1サイクル、Tm*m1が20サイクルとなり平均命令実行時間は21サイクルとなる。つまり、1次キャッシュを設けることにより性能は4倍以上に向上したことになる。しかし、まだ、メモリアクセスの待ち時間がプロセサコアの実行時間の20倍という状況であり効率が悪い。

次に、2次キャッシュを設ける場合を考える。1次キャッシュのミス率をm1、2次キャッシュのミス率をm2、1次キャッシュをミスして2次キャッシュをヒットした場合の待ち時間をTm12、2次キャッシュもミスしてメモリからデータを持ってくる時間をTmとすると、CPIは、

CPI=Ccore+Tm12*m1*(1-m2)+Tm*m2

と表わされる。Tm12 は典型的な値として10サイクル、大容量2次キャッシュの場合のm2は0.1%~1%とすると、Ccoreは約1サイクル、第2項も約1サイクル、第3項はm2が0.1%の場合は0.2サイクルとなり、平均命令実行時間は2.2サイクルとなる。一方、m2が1%の場合は、第3項は2サイクルとなり、全体の平均命令実行時間は4サイクルとなる。従って、1次キャッシュだけの場合に比べて、大容量の2次キャッシュを設けることにより5倍から10倍の性能向上が達成され、メモリ待ち時間とプロセサコアの実行時間をおおよそ同程度の値とすることが出来る。

しかし、2次キャッシュミスが大きいプログラムでは、2次キャッシュの容量を更に大きくしてm2を下げるか、あるいは、さらに容量の大きな3次キャッシュを設けてミス率を下げてメモリアクセス頻度を減らすことが必要となる。データベースなどのビジネス系の大規模アプリケーションは大きなメモリ領域をランダムにアクセスする2次キャッシュミス率の高いプログラムであり、これらを効率よく実行することが求められるサーバ用プロセサでは、2次キャッシュを大容量化したり、速度は落ちるが更に大容量の3次キャッシュを使用したりする構成が一般的である。

つまり、キャッシュミスが大きいプログラムを実行する場合にはコアを複雑にしてCPIを減らしたり、クロックを上げても性能は殆ど改善されず、性能を改善するためには、キャッシュのミス率の低減と、下位のキャッシュやメモリのアクセス時間を短縮することが重要である。

一つ注意すべきことは、ここで述べたCPIの計算式は、1次キャッシュをミスするとデータが到着するまでコアでの処理はストップするという単純なプロセサを想定して作られているが、最近のプロセサでは命令の先読みをしたり、データアクセスについてもキャッシュミスがあっても、そのデータに依存しない次の命令をどんどん実行し続けるというようなOut-of-Order処理を行ったりしており、このオーバーラップの時間を待ち時間Tm*から差し引くような補正が必要である。

コンピュータアーキテクチャの話 (27) マイクロプロセサの実装コスト

論理回路の遅延時間とクロック周波数

論理回路の遅延時間とクロック周波数

各論理回路の入力容量が一定となるようにゲートを設計すると、ゲートの遅延時間は負荷となるゲートの個数(あるいは大きさ)が何個であるかという電気的な増幅率(Electrical Effort)とLogical Effortの積(Total Effort)で決まるというのがLogical Effortの理論である。ゲートを多段に接続する場合、各段のTotal Effortを小さくして全体のゲート段数を増やしても、各段のTotal Effortを大きくして全体のゲート段数を減らしても、トータルの遅延時間は大きくなり、各段のTotal Effortを4程度とすると遅延時間が最小になることが知られている。

しかし、各段のTotal Effortをこれよりも若干大きめの5~8程度に取ることにより、遅延時間は若干増加するが、消費電力は遅延時間の増加分より大きく低減する。このため、低電力を重視する場合には4よりも多少大きめのTotal Effortとなるように設計する方が良い。

2入力NANDゲートのLogical Effortは4/3であるので、単位入力容量のゲートを3個負荷として接続するとTotal Effortは、(4/3)*3=4である。また、インバータに単位入力容量のゲートを4個負荷に接続した場合もTotal Effortは1*4=4である。後者はFan Out 4(FO4と略称される)インバータとも呼ばれ、半導体プロセスのゲート遅延時間を表わす代表値として使われる。そして、プロセサのマイクロアーキテクチャを議論する場合には、パイプライン1段あたりFO4インバータ何段分の遅延時間で構成するかというように使われる。

上記の計算は配線の寄生容量を含んでいないが、配線容量は、ゲートの単位入力容量を基準として、入力、何個分というように換算される。配線の寄生容量は微細化のレベルにはあまり影響されず、1mmあたり100~200fF (Femto Farad)程度となるのが普通である。トランジスタのゲート容量は、微細化によりゲート絶縁膜が薄くなるが、一方、ゲートポリシリコンの幅も減少するので、微細化のレベルに拘わらず、チャネル幅1umあたり1fF程度である。仮に、W=0.8μmのP-TrとW=0.4μmのN-Trで構成されるインバータを基準とすると、単位入力容量は1.2fFとなり、6~12μmの長さの配線が1ゲート入力と等価として計算される。

スーパースカラプロセサでは命令のフェッチからデコード、実行、結果の格納までのトータルの論理はFO4インバータ換算で250~300段程度であり、パイプライン1段あたりで複雑な論理を実行して25FO4程度とすると10~12段程度のパイプライン構成になる。65nmテクノロジのFO4インバータの遅延(=FO3 2NAND)は、ITRSロードマップでは16psであり、25FO4の場合は400psとなり、単純計算ではクロックは2.5GHzとなる。一方、最高クロックを追求するPentium 4やCellプロセサの設計では各パイプステージを12~14FO4で構成している。この設計では、単純計算では200ps程度の遅延であり5GHzのクロックとなる。但し、実際にはパイプラインの間にフリップフロップを入れる必要があり、このフリップフロップ回路の遅延時間とクロック分配の時間ずれ(Clock Skew)として3FO4程度が加わるので、前者は2.2~2.3GHz、後者は4.2GHz程度となる。非常に粗い見積もりであるが、このクロック周波数は、65nmプロセスで作られる次世代のRISCプロセサとクロック重視のPentium 4やCellなどのプロセサのクロック周波数としてほぼ妥当な値である。

ここまでは負荷容量の充放電による遅延時間だけを考慮してきたが、微細化に伴い配線のRC遅延が大きな遅延時間を占めるようになってきている。

RC線路の伝送波形

この図に示すように、送端のゲートの出力では鋭い立ち上がりの波形であっても、配線の抵抗と寄生容量からなるRC線路を伝送していく内に、波形が鈍ってしまう。抵抗が無い場合は、青色で示したような波形であり、抵抗分があることにより大きな遅延が発生する。配線全体の抵抗をR、寄生容量をCとすると、この遅延は、おおよそ、RC/3となる。RとCはともに配線の長さに比例するので、RC線路の遅延は配線長の2乗に比例する。

LSI内部の配線のRC遅延の値は、ITRSロードマップの65nm世代の半導体プロセスでは、長さ1mmの銅配線の場合、最下層の第1層(136nmピッチ)では767ps、中間層(140nmピッチ)では682ps、上層の幅が広い配線(210nmピッチ)では209psとなっている。

上層の幅の広い配線はRC遅延が小さく、同一の配線遅延を許容するとより長い距離の信号伝送を行うことが出来る。しかし、使用できる配線本数は線幅に逆比例して減少するので、全ての信号を上層で配線することは出来ず、遅延時間の厳しいところに限定して使用するのが一般的である。

しかし、2GHzのクロックの場合、1サイクルの時間は500psであり、上層の配線を使っても1mmの配線のRC遅延は1サイクルの40%以上を占め、2mmになると1サイクルでも伝送できない。そこで配線遅延を減らすためには、次に示すように、配線を分割して、間にリピータ(インバータやバッファなど)を入れるという手法が用いられる。

コンピュータアーキテクチャの話 (318) GPUはどうやってマルチスレッド処理を行っているか

GPUのマルチスレッド処理

GPUのマルチスレッド処理

GPUでは多数の頂点やピクセルの処理を、それぞれのスレッドで並列に実行する。つまり、演算器の数だけの、100~数1000スレッドを並列に、SIMT方式で実行する。これに加えて、歴史的なマルチスレッドマシンのところで紹介したHEPのように、多数のスレッドのグループを切り替えて順番に処理すると、同じスレッドに戻ってくるまでの時間が長くなるので、Out-of-Order実行などの複雑な制御を使わなくても、演算器のレーテンシやメモリアクセスのレーテンシを隠すことができる。

GPUでは、この両者の効果を有効に利用しており、演算器数の数10倍のオーダのスレッドを同時並列的に実行する。こうすると、各演算器は数10スレッドを切り替えて実行することになり、同じスレッドの次の命令を実行するのは数10サイクル後となり、演算やロード/ストア(キャッシュヒットの場合)のレーテンシを隠すことができる。

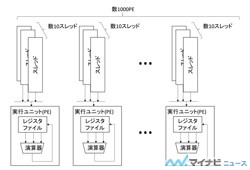

しかし、このような実行を行うためには、数1000個の演算器を持つハイエンドGPUの場合は、数万個以上のスレッドを並列に実行する必要がある。このような実行を行うハードウェアの基本的な構造は、図3.2のようになる。

図3.2 数万個以上の並列スレッド実行の考え方

しかし、すべてのスレッドが頂点の座標変換や同じアルゴリズムを使うピクセルシェーディングを行う場合は、それぞれの実行ユニット(PE)に数10スレッドをサイクルごとに切り替えながら命令を供給する機構を付けるのは無駄が多い。このため、NVIDIAのGPUでは32PEのグループに同じ命令を供給している。一方、AMDのGPUでは64PEのグループに同じ命令を供給している。

図3.3に示すように、命令発行機構を32PEで共通にすると、命令発行に必要なハードウェアが大幅に減少し、多数の実行ユニットをチップに詰め込むことが可能になる。これが、GPUが高い演算性能を持つことができる大きな理由である。

図3.3 命令供給機構を32PE単位に簡略化した構造

チップ上の数1000個のPEが全く同じ命令列を実行する場合は、32PEごとに命令発行機能を付ける必要もなく、数1000PEまとめて、1つの命令発行機構でも良い。しかし、ある程度、命令の発行にフレキシビリティを持たせた方が良い場合がある。

例えば、if文がある場合は、SIMT実行では、それぞれのスレッドで条件判定を行い、次の命令を実行するかどうかを決めるが、図3.3の構造で一組の32PE全部が、条件が不成立の場合は、演算結果を書き込まない命令を全部のPEが実行するのは無駄で、if文の次の文にジャンプしてしまえばよい。しかし、隣の32PEのグループでは条件が成立するPEがあるとすると、そのグループでは同じようにif文の次の文にジャンプしてしまうわけには行かない。数1000個のPE全部に命令供給が共通の場合は、その中のどれか一つのPEでも条件が成立する場合は、全てのPEがif文の命令を実行する(ただし、結果の書き込みは条件ビットで制御する)必要があるが、32PE単位で命令を供給する場合は、そのグループ内のすべてのPEで条件が不成立ならジャンプしてしまえるので、無駄な命令の実行を抑えることができる。

また、一画面の中でも、重要な部分には高度なアルゴリズムを使って綺麗な絵を作り、背景の部分は簡単なアルゴリズムで済まして、描画時間を短縮するという場合は、全てのPEが同じ命令を実行するのではなく、PEのグループごとに異なる命令を実行する必要がある。

さらに、最近では迫真の動きを表現するため、破壊されて砕け飛ぶ瓦礫の動きや、波立つ水の動きなどを、アーティストの描画ではなく、物理的に動きをシミュレーションして求めるということも行われている。このような場合も、一部のPEを物理シミュレーション用に割り当て、別のプログラムを実行させることが必要になる。

これらの使い方を考えると、1つのチップ上の数1000のPEに1つの命令供給機構ではなく、ある程度のPEのグループ単位で命令供給機構を設けて置く方がよい。このため、NVIDIAのGPUでは32PEを単位としており、これをワープ(Warp)と呼んでいる。なお、ワープはSFの宇宙船が行う空間ジャンプではなく、命令列を織物の縦糸(スレッド)に見立てて、それと直交するする横糸(ワープ)という意味である。また、AMDは64PEを単位としており、これをWavefrontと呼んでいる。

ここではワープを処理するためには32個のPEが必要と書いてきたが、NVIDIAのFermi GPUでは、図3.4に示すように、サイクル0ではワープ0の命令1を使って論理PE0 のレジスタを読み出し、サイクル1でこの命令を実行するのであるが、次のサイクル1でも同じ命令を使って論理PE1のレジスタを読み出し、サイクル2でその命令を実行するという形で、1つの物理PEに2サイクル連続して同じ命令を実行させて、論理的には2つのPEに見せている。

図3.4 1つの物理PEを複数の論理PEに見せる

このため、Fermi GPUでは、ワープを実行する資源は16個の演算ユニットからなっている。このようにすると、2サイクルに1命令を実行ユニットに発行すれば良いので、命令発行ユニットの設計は楽になる。

しかし、32論理PEの演算の実行には1つの命令が必要であるという点は変わらず、1ワープの実行に2サイクル掛かるので、命令の発行も2サイクルに1回で良いことになっているだけで、このような構造が、必ずしも得とは言えない。

このためか、昔のNVIDIAのTesla GPUは4サイクル連続して、同じ命令を実行していたのであるが、Fermi GPUでは2サイクルとなり、現在のKepler GPUや最新のMaxwell GPUでは、遂に1サイクルになってしまった。ただし、Maxwellでも演算器に比べて使用頻度の低いSFU(Special Function Unit:三角関数などの計算ユニット)とロード/ストアユニットは4サイクル実行となっており、使用頻度の低いユニットでは物量を減らす設計になっている。

なお、AMDのGCN(Graphic Core Next) GPUは16個の演算器が4サイクル同じ命令を実行することにより64要素のWavefrontを処理する構造となっている。

CPUに比べて圧倒的に多いレジスタ数

安川電機、ジャカルタにロボットセンタ開設

安川電機は11月27日、インドネシア・ジャカルタ市内にインドネシア・ロボットセンタを開設したと発表した。

豊富な天然資源を背景とした経済成長が見込まれるインドネシアにおいて、現地での自動化ニーズが高い自動車・二輪車・建設機械・食品・医薬品・化粧品などの市場に向けて各種ロボットソリューションの提案力強化を図る。

同施設の延床面積は1400m2で、2フロア構成。顧客にロボット操作教育、保守教育を提供するとともに「来て・見て・触って」をコンセプトに、実機を使ったデモやテストを通じて、ロボットへの理解を深めることを目指す。

また同施設では、ロボットを使った自動化設備の設計・製作を請け負うシステムインテグレータ(SI)へのロボットに関する最新情報の提供や教育などのサポート体制も強化される。SIルーム・SIラボにて、ロボット実機による教育を実施し、機能を理解してもらうなど、SIとの関係強化も推進する。

インドネシア・ロボットセンタ