仕事で役立つ人気ビジネスアプリおすすめ!

[PR]

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

京大、光でデザイン可能なテラヘルツデバイスを開発

京都大学(京大) 学際融合教育研究推進センター次世代開拓研究ユニットの岡田隆典助教らの研究グループは、周期的なパターンをしたフェムト秒パルスレーザーを半導体表面に照射することでテラヘルツデバイスを作製し、このデバイスを用いて、テラヘルツ光の広帯域変調を実現したことを発表した。同成果は、英国科学電子雑誌「Scientific Reports」に掲載された。

テラヘルツデバイスは一種の光誘起構造体であり、空間分布が周期的になったフェムト秒パルスレーザーを高抵抗シリコン半導体表面に照射することで作製される。

光デザインテラヘルツデバイスの作製方法。成形された励起フェムト秒パルスによって半導体プリズム表面上に2次元金属構造が作製される。また、プローブ光としてテラヘルツ光を用いている

この空間パターンは空間光変調器によって自由に作ることができ、簡単に形状を変えることができる。すでに発生と検出技術が確立したテラヘルツ光と呼ばれる新しい光を用いて反射光を観測した結果、特徴的なディップが現れることが判明しており、このディップは、平面金属構造表面からの光応答であることが確認されている。

この結果は、フェムト秒レーザー照射するとシリコン表面にレーザー形状と同じ金属構造が作製され、レーザー照射を止めるとその金属構造が消滅することを意味している。つまり、光のパターンを自由に書く、または消すことで、構造が出現または消滅することを実現したというもので、広帯域の光変調も可能だという。

テラヘルツ反射率のグラフ。図中のaは周期構造の周期。構造体による特徴的なディップが観測されている。周期を変えるとディップ周波数が大きく変化し、広帯域周波数変調を実現する。構造が無い場合はディップが現れない

さらに、同技術はテラヘルツ光を操作する手法としても期待されている。フォトニック結晶やメタマテリアルなど光を操作する人工構造体は、今まで微細加工技術や電極接続が必要だったが、今回の研究で開発されたテラヘルツデバイスは、そうした加工技術や電極を必要としない光デバイスで、10万分の1秒でデバイスを作製、変形、消去できるため、デバイスをリアルタイムに何度も書き換えることが可能なため、電気を使わず光のみで動作する技術として応用展開することが期待できるという。

ST、TSV技術を採用し小型・スマート化したMEMSチップの量産を発表

STMicroelectronicsは、MEMSの量産にTSV(Through-Silicon Via)技術を採用したことを発表した。これにより、スマート・センサや多軸マルチセンサ・モジュールなど同社のマルチチップMEMS製品に使用される配線を従来よりも短く垂直な配線に置き換えることが可能となり、より小型サイズで高水準の機能統合ならびに高性能化が実現可能になると同社では説明している。

TSVは、パッケージ内で垂直に重ねられた複数のSiダイを接続することで、ワイヤ・ボンディングやフリップチップ・スタッキングよりも優れたスペース効率および高密度配線を実現する技術。同社が特許を保有するTSV技術はすでにMEMSチップの量産に適用されており、チップサイズの小型化と共に、堅牢性と性能の向上に役立っているという。

なお、同社では現在までに自社のMEMSセンサの累積出荷数は16億個を突破し、コンシューマ、コンピュータ、自動車、産業および医療分野における各アプリケーションに採用されていると説明している。

TSVを活用したSTMicroelectronicsのMEMSチップのダイ写真

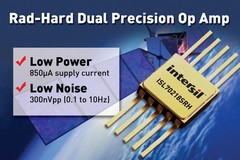

Intersil、耐放射線特性を備えたデュアル回路のオペアンプを発売

Intersilは、耐放射線(Rad-Hard)特性を備えた単一電源動作のオペアンプ・ファミリ製品「ISL70218SRH」を発売した。

同製品はデュアル回路構成のレールツーレール出力アンプで、ダイナミックレンジを最大限に確保できるようになっている。消費電力を競合製品のおよそ半分に抑えているほか、消費電流としては、人工衛星アプリケーションにも搭載できるように、850μAとなっている。

さらに、入力ノイズ300nVp-p(0.1Hz~10Hz)という高いノイズ性能を実現している。また、入力オフセット電圧、入力バイアス電流などにおいて、優れた性能を達成、低線量率および高線量率のいずれの条件でも安定した動作が可能となっている。

なお、同製品は10ピンのセラミックフラットパックで供給され、サンプル価格は58.90ドル。人工衛星、原子力発電所設備、油田設備のほか、軍用温度範囲と耐湿パッケージを必要とするアプリケーションを対象としている。

「ISL70218SRH」

Infineon、パワー半導体向け300mm薄ウェハ技術でのチップ生産に成功

Infineon Technologiesは、オーストリアVillachの生産拠点で、パワー半導体向け300mm薄ウェハによるチップ初期生産に成功したことを発表した。

今回のチップは、評価結果より200mmウェハで製造されるパワー半導体と同一の動作特性を示している。

同社は2010年10月、Villachにおいて、300mmウェハ/薄ウェハ技術による、パワー半導体のパイロットラインの開設に着手。現在までに、研究開発、生産技術、マーケティングの各分野から集まった50人のエンジニアと物理学者で構成されたチームにより、研究開発、試作が進められてきた。

また、同社は投資計画の一環として、2011年7月末に、ドイツDresdenを300mmウェハによるパワー半導体生産技術(Power300)向けの量産拠点とすることを発表しており、まずは2014年までの間に約2億5000万ユーロの投資を行い、約250人の雇用を創出する計画である。

パワー半導体向け300mm薄ウェハ

高性能な3Dグラフィックス描画をFPGAで手軽に実現できるPICA 200 for FPGA

ニンテンドー3DSのグラフィックスや、オリンパスの第3世代マイクロフォーサーズ(マイクロ一眼)「E-P3/E-PL3/E-PM1」のGUI向けにグラフィックスIPコアを提供しているディジタルメディアプロフェッショナル(DMP)。同社とFPGAベンダXilinxの日本法人ザイリンクスは2011年8月に、XilinxのハイエンドFPGA「Virtex-6」ファミリを搭載した3D/2Dグラフィックスシステム開発評価ボードとDMPの3D/2DグラフィックスIPを統合した「PICA 200(SMAPH-F) for FPGA Virtex-6 Evalution Kit」を発表した。これにより、手軽に3Dグラフィックスの開発が可能になると両社は語っている。今回、DMPとザイリンクスの双方に話を聞く機会を得たので、その様子をお伝えしたい。

そもそもDMPは2002年7月に法政大学の池戸恒雄教授により設立されたベンチャー企業で、3D/2DグラフィックスIPの開発とライセンスビジネスを展開してきており、上記のようなコンシューマ機器などへの搭載も進み、業績も好調なことから2011年6月には東京証券取引所マザーズ市場への上場を果たしている・

同社のグラフィックスIPのラインアップは大きく分けて4種類に分けられる。高機能かつ高性能な3Dグラフィックスを表現可能な「リアリスティック3Dグラフィックス」用IP「PICA 200」、一般的な用途向け「3Dグラフィックス/コンピューティング」用IPとして「PICA 200 Lite」「SMAPH-S」、そして「PICA 200 for FPGA」の3つ、「2Dベクターグラフィックス」用IP「SMAPH-F」、そして最後は「ベクター/3Dグラフィックスハイブリッド」用IP「SMAPH-H」だ。

DMPの提供しているIPラインアップ

3D系のIPは基本的にPICA 200がすべてベースになって開発されたもの。PICA 200はOpenGL ES 1.1に対応しているほか、独自技術でゲーム系グラフィックスに特化した「DMP MAESTROテクノロジー」を採用(現在は第2世代となる「MAESTRO 2G」を採用)することで、低消費電力を実現しつつ、相当の3D描画性能を達成していることは3DSに採用されたことなどからも窺えるだろう。

PICA 200の概要。同社のIPの最大のポイントはロジック領域が少なく、かつ他社のグラフィックスコアと比較しても低消費電力だというところ

PICA 200 LiteはPICA 200からMAESTROを除外し、UIアプリ向けに機能最適化を図ったIP。フルHD解像度に対応でき、フレームバッファは最大4088×4088ピクセル、ピクセルフォーマットはRGBA4444、RGB565、RGBA5551、RGBA8888に対応し、頂点性能は最大12.7Mピクセル/秒(166MHz動作時)、ピクセル性能は最大166ピクセル/秒(166MHz動作字)となっている。

PICA 200 Lite/PICA 200 for FPGAの概要

このPICA 200 Liteの性能強化を図り、OpenGL ES 2.0に対応させたのがSMAPH-Sだ。プログラマブルシェーダに対応し、頂点性能は最大106Mポリゴン/秒(266MHz、4頂点処理プロセッサ搭載時)、ピクセル性能は最大2.2Gフラグメント/秒(266MHz、8フラグメント処理プロセッサ搭載時)となっている。こちらは今後、OpenCL 1.1への対応を予定する次世代IP「SMAPH-S Next(開発コード名)」も開発が進められているという。

OpenGL ES 2. に対応したプログラマブルシェーダ・プロセッサを搭載したSMAPH-Sの概要。用途に応じて柔軟にプロセッサ数とパイプライン本数を変更することが可能で、表ではコア数は24、パイプライン数は4本までとなっているが、それ以上に搭載することも可能だという。ちなみにS404クラスで、PlayStation VitaのGPUと同等の描画性能だとDMPでは説明している

2D向けのSMAPH-FはOpenVG 1.1に準拠しており、インタフェースとして活用することで、Adobe Flash LiteやSVGなどのベクターグラフィックスライブラリのハードウエア・アクセラレーションが可能となる。また、SMAPH-HはおおむねSMAPH-SとSMAPH-Fを統合したIPという位置づけとなっている。

SMAPH-Fの概要

SMAPH-Hの概要

そして今回の話題であるPICA 200 for FPGAだが、FPGAでの利用向けに特化したIPで、最大XGA解像度に対応し、頂点性能は最大3.8Mポリゴン/秒(50MHz動作時。Virtex-6ではこれが最高値だが、Virtex-7になればもっと高速な処理ができるようになるという)、ピクセル性能は最大50Mピクセル/秒(50MHz動作時)のレンダリングが可能で、汎用GPUやASICで実現していた3Dグラフィックス描画をFPGA上で実現することが可能となるというもの。対応FPGAはXilinxのVirtex-5/6のほか、28nmプロセスを採用した次世代FPGAである「Xilinx 7シリーズ(Virtex/Kintex/Artix-7)」にも対応する。

PICA 200 for FPGAの評価ボードは東京エレクトロン デバイス(TED)が開発を担当しており、基板上にはFPGAとして最大規模の集積度を誇る「Virtex-6 LX760」とPCI Express ×4 Gen1用に「Virtex-6 LX550T」の2つのFPGAが搭載されており(LX550Tの余ったロジックセル部分にほかのIPを搭載することも可能)、x86やARM、MIPSなどの各種プロセッサとのやり取りをしながら、3D GUIなどの開発を行うことができる。

赤いボードがPICA 200 for FPGA。デモではその上にARMコア搭載ボードとLCDを載せつつ、ARMコアを使わずにAtomベースのx86アーキテクチャでPCI Express経由で3D描画のデモを見せていた。そんな構成でも、それなりに3D描画がグルグルと動いており、作成したUIなどの動作チェックなどとしては十分な性能だと思われた

同ソリューションが狙うのは主に2つのカテゴリ。1つは従来からFPGAが得意としてきたSoC/ASICのプロトタイピング。そしてもう1つは少量品で、ASICなどを作るまでもない分野。例えば航空宇宙分野などは機体そのものの生産数も少ないことから、ASICをいちいち作っていては採算に見合わない。そういった分野も従来からFPGAが活用されてきているが、そうした領域でのより高度なGUIの実現ニーズに対応することが可能となる。

具体的には、ハードウェア/ソフトウェアエンジニアによる開発現場での活用のほか、UIをデザインするデザイナーそのものにも使ってもらいたいとしている。実際にデモも見せてもらったが、組込機器などのUIとして考えれば十分な性能を実現しているように思えた。

また、将来的にはXilinx 7シリーズを用いることで、民生機器などでの活用に向けた開発も可能になると両社いずれもが期待を語っている。

さらに、PICA 200 for FPGAという名前での販売だが、ほかのDMPのIPも別途ライセンスを受けることで搭載することが可能(MAESTRO含む)であるため、必要に応じて、それらのIPも活用した開発も可能となっており、より高度なUIの実現なども可能となる。

なお、すでにSMAPH-F for FPGAの方は活用に向けた交渉が進められているとするほか、PICA 200 for FPGAについても販売初年度では10ライセンスの販売を目標としており、3Dグラフィックスの適用分野の拡大を目指した取り組みを今後も進めていくとしている。