仕事で役立つ人気ビジネスアプリおすすめ!

[PR]

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

富士通研ら、CMOSプロセス採用パワーアンプ向け高耐圧トランジスタを開発

富士通研究所ならびに富士通マイクロエレクトロニクスは12月17日、CMOSロジックプロセスを用いたワイヤレス機器用パワーアンプ向け高耐圧トランジスタを開発したことを発表した。

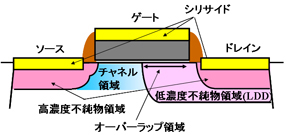

従来、WiMAXなどの高周波向けパワーアンプに要求される出力電圧を実現するためには、通常のCMOSロジックプロセスによるトランジスタでは耐圧が不十分であった。そのため、CMOSロジックプロセスとの親和性を保ちながら、トランジスタの破壊につながるドレイン付近の電界を緩和させた構造を採用し、トランジスタの高耐圧化を行う必要があった。また、従来の高耐圧構造はトランジスタのオン抵抗を上昇させてしまう問題も抱えていた。富士通研らは、トランジスタのドレイン側に不純物を低濃度で注入した領域(LDD:Lightly Doped Drain)を形成し、その領域をゲートとオーバーラップさせることで、ドレインに加わる横方向の電界とゲート酸化膜に加わる電界を緩やかにし、耐圧の向上を実現した。

また、トランジスタのチャネルの不純物分布を、横方向に勾配を持たせることにより、ドレイン側のチャネル不純物濃度を低減させ、オン抵抗の主要因であるドレイン抵抗の上昇を抑制、同時にドレインに加わる横方向の電界の低減により、耐圧を向上させた。

開発したトランジスタの構造

これらの技術を採用したトランジスタは、従来のCMOSトランジスタの耐圧向上技術であるゲート/ドレインの間隔を広げる方法と比べても、オン抵抗の上昇を抑えることが可能であることが確認された。

製造方法については、通常の3.3VのI/Oトランジスタの製造工程に、LDD領域の形成工程と専用チャネル領域の形成工程を追加のみで製造が可能。

今回、45nmプロセスの製造技術を用いて、通常の3.3VのI/Oトランジスタに同技術を適用したところ、耐圧を6Vから10Vに引き上げることに成功。トランジスタ特性としては、最大発振周波数が43GHzで、ゲート幅1mmあたり0.6Wの最大電力を達成したほか、基本的な信頼性評価でも良好な結果が得られたという。

パワートランジスタの特性(測定周波数2.1GHz, ゲート幅0.32mm)

今後、両社は、同技術の発展を目指し、パワーアンプと制御回路の1チップ化を図ったパワーアンプモジュールの提供を目指すとしている。