仕事で役立つ人気ビジネスアプリおすすめ!

[PR]

[PR]上記の広告は3ヶ月以上新規記事投稿のないブログに表示されています。新しい記事を書く事で広告が消えます。

コンピュータアーキテクチャの話 (248) プロセサ内部におけるデカップリングキャパシタ

プロセサチップ内のデカップリングキャパシタ

プロセサチップ内のデカップリングキャパシタ

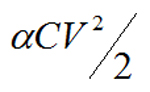

消費電力の項で書いたように、プロセサの消費電力には負荷容量の充放電によるダイナミック電力とトランジスタのリークによるスタティックな電力がある。このダイナミック電力は

である。このαはどの程度の回路がスイッチするかの比率であるが、ハイエンドのマイクロプロセサではチップ全体でみると数%程度しかスイッチしていない。

各信号線が毎サイクルランダムに0、1の値を取るとすると、0→1、1→0と0→0、1→1が等確率で起こるので、αは0.5になるはずである。しかし、メモリアクセスが無い場合はキャッシュの回路は動作していない、整数演算の時は浮動小数点ユニットは動作していないなど、それぞれの時点には使用していない回路が多くあることと、リザベーションステーションやロードストアキューなどのエントリでも常にフルに使われているわけではなく、その時点で使用していないエントリではタグマッチなどは不要というように、使用されない回路が多く存在するのでαは0.05かそれ以下になってしまう。

αが0.04、クロックが2.66GHz、電源電圧が1.1Vでダイナミック電力が70Wのプロセサを想定すると、C=2×70/(0.04×1.21×2.66×10e+9)=1087×10e-9でCは1087nFということになる。

図3.13の右側に書かれたその時点ではスイッチしていない回路の出力が0の場合は青線、1の場合は赤線の経路で、負荷容量の半分(Cl/2)のキャパシタンスとオンになっている側のトランジスタを直列に接続したものが電源線とグランド線の間に接続されている。左側の回路がスイッチし電源線から電流を引き込むと、これらのスイッチしていない回路は電流を供給する電源のデカップリングキャパシタとして動作する。

図3.13 スイッチしていない回路の負荷容量は電源のデカップリングキャパシタになる

チップ全体で1087μFの負荷容量があるとすると、スイッチしていない回路の半分の500μF程度のデカップリングキャパシタが付いていることになる。また、これ以外に各トランジスタのソースとボディ間のように直接電源とグランドの間につながっているダイナミック電力に関係しない容量がある。これを含めると、まあ、0.6μF程度のデカップリング容量であろう。この容量の1GHzでの1/ωCは、0.265mΩとなる。ということで、バンプを経由したパッケージ接続の部分が2GHzまで0.5mΩを下回ることができれば、それ以上の周波数はチップ内のキャパシタでカバーできるという計算になる。

しかし、これはチップ全体の平均の話で、負荷容量の大きなクロックバッファやバスなどを駆動する部分が同時にスイッチすると、局所的には、数10psの立ち上がりで大きな電流が流れる。このように短時間で電流変化が起こると、電源供給系はキャパシタンスの大きなRC線路であるので、スイッチした回路から離れた場所のキャパシタからの電荷の供給は間に合わない。このため、その部分では局所的に電荷の供給が不足して電源電圧の低下が起こってしまう。このような問題を避けるために、大きな電流が流れる部分の近傍にデカップリング専用のキャパシタセルを配置する。

LSIの中で単位面積あたりのキャパシタンスが最も大きいのはゲート絶縁膜を使うキャパシタであり、キャパシタセルは図3.14のように作られる。

図3.14 キャパシタセルの構造

キャパシタセルはゲート電極を電源に繋ぎ、トランジスタのソース、ドレインに相当する電極をグランドに繋ぎ、トランジスタのゲート容量と同じでゲート電極とシリコンの表面にできた反転層の間のキャパシタンスを利用する。一般に、キャパシタンスを大きくするためにドレインとソース間の距離を大きくとる。しかし、シリコン表面にできる反転層の抵抗は大きいので、この距離をあまり長くすると直列抵抗が増えてしまい高速に電荷を供給することができなくなる。

前述のクロックバッファなどのようにpsオーダで電荷の供給が必要な場合は、ソース、ドレイン間の距離はロジックトランジスタと同じか、せいぜい、2倍程度に抑える必要がある。一般的に電源のデカップリング容量として利用する場合はもっとソース、ドレイン間の距離を大きくしてよいが、あまり大きくし過ぎると直列抵抗の大きい中央部分は有効に働かなってしまうので、逆に、面積の無駄遣いになってしまう。ということで、ロジックトランジスタの5~10倍程度のソース、ドレイン間距離が使われる。

電源ノイズを減らすという観点からは、電源のデカップリングキャパシタは多いに越したことはなく、論理ゲートが置かれていない空き領域をキャパシタセルで埋め、数100nFのデカップリングキャパシタを追加するという設計も良く見られる。

従来はこのような設計で良かったが、使用していない部分の電源を切るパワーゲートが使われるようになると、少し事情が変わってくる。パワーゲートされた部分はスイッチをしていない回路であるが、電源から切り離されているのでデカップリングキャパシタとしては動作しなくなる。つまり、パワーゲートの状況でデカップリングキャパシタの量と、どこに付いているかが変わってくる。このため、各ブロックがパワーゲートされるすべてのバリエーションに対して、電流変化量とデカップリングキャパシタの必要量が満たされているかを確認する必要がある。このため、パワーゲートの状態に拘わらず常に電源に接続されているキャパシタセルの重要性が増している。